CS Mantech: Empowering power devices

Novel material combinations and innovative architectures take GaN and Ga2O3 power devices closer to fulfilling their full potential.

BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

Look up the physical properties of a range of semiconducting materials and it’s easy to understand why SiC and GaN are more attractive than silicon, and why Ga2O3 holds so much promise. But getting transistors and diodes made from these wide and ultra-wide bandgap materials to get close to fulfilling their true potential, rather than just outperforming silicon, is far from easy. Success demands improvements to the design of these devices, along with the processes for producing them.

Thanks to the efforts of researchers from all over the world, steady progress is being made on improving the performance of many devices made from many of the key materials that have a bandgap that’s wider than that of silicon. Gains are seen in the pages of journals, as well as in the presentations delivered at many conferences, including this year’s CS Mantech. At that gathering, held in New Orleans from 19 to 22 May, a number of speakers showcased advances in power electronic devices, with papers including those reporting gains from pairing GaN with tungsten and with NiO, and promising architectures, such as GaN diodes with nitrogen-ion implantation and Ga2O3 finFETs.

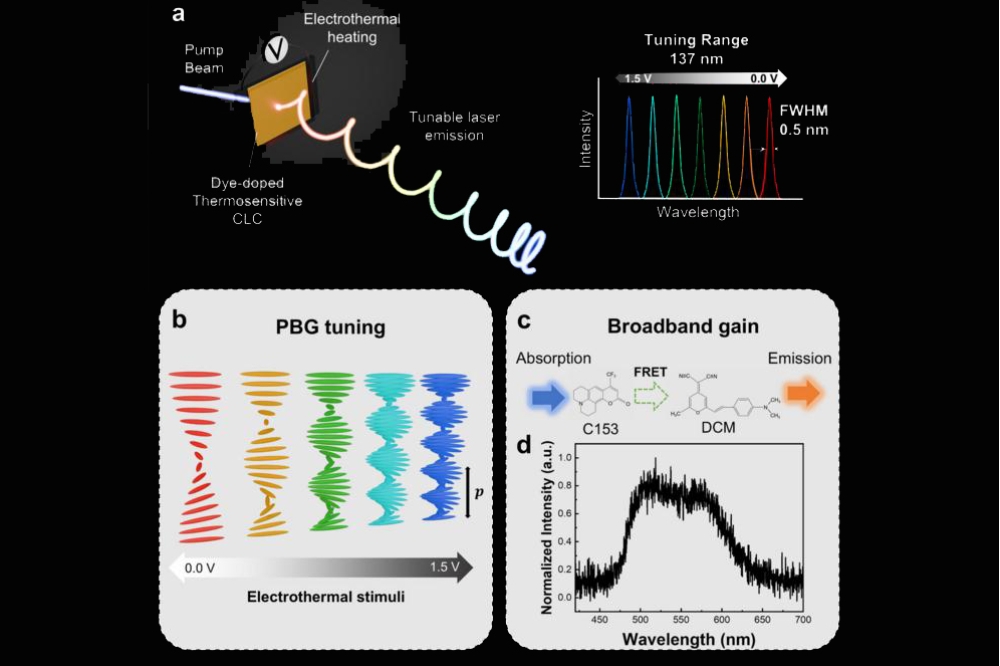

Figure 1. To produce vertical GaN-on-tungsten p-n diodes, the German collaboration led by FBH Berlin employs a wafer back-end process that involves: (a) epitaxial wafer bow reduction, (b) front-end electronic device manufacturing, (c) temporary sapphire carrier bonding, (d) laser lift-off of the GaN epitaxy membrane from the sapphire substrate, (e) the addition of GaN backside N-face ohmic contacts and bonding metal deposition, (f) GaN membrane and tungsten wafer metal bonding, (g) temporary carrier removal, and (h) the formation of the GaN membrane on the tungsten substrate.

GaN-on-tungsten diodes

Within the power electronics sector of our industry, SiC generates the most significant revenue. However, sales have not soared as fast as many have been hoping for, and from a commercial perspective, GaN is receiving a great deal of attention.

GaN HEMTs have already established a ‘killer’ application, due to their deployment in fast chargers for mobile devices. Sales of this class of transistor involve the lateral variant, which is relatively straightforward to produce. But a switch to a vertical geometry promises substantial gains in performance, alongside reduced chip costs that come from miniaturisation.

For lower-voltage products, the compromises that come from a lateral geometry are less troublesome, with HEMTs with a 100 V rating having a typical resistance of around 3 mW cm-2. However, when this geometry is used for 650 V devices, the chip size increases, and resistance can be five times as high. For this voltage rating, vertical devices have much appeal, being around one-tenth of the size of their lateral counterparts and having a resistance of just a few mΩ cm-2.

At CS Mantech, a collaboration led by researchers at FBH Berlin, and involving engineers from the Fraunhofer Institute for Laser Technology and EV Group, presented their latest efforts in developing vertical GaN power devices with blocking voltages of 1 kV or more. This requirement demands n-type drift layers more than 10 µm-thick, which can lead to a number of issues when growth is undertaken on a foreign substrate. Due to lattice and thermal mismatch, there can be an increase in the threading dislocation density and leakage current, as well as mechanical strain and fragility.

At last year’s CS Mantech, this team reported steps they had taken to address these concerns, describing the wafer bow reduction through laser stealth scribing of the sapphire substrate.

Now they have built on this previous success, removing the electrically and thermally insulating sapphire substrate from the GaN membrane electronic devices, and bonding them to tungsten.

Speaking to Compound Semiconductor on behalf of the collaboration, Enrico Brusaterra from FBH Berlin explained that the team could have employed any conductive metal for their work. “However, we chose tungsten, as it has a thermal expansion coefficient almost identical to GaN.”

Brusaterra believes that tungsten substrates offer good levels of availability and affordability. “Although more than 80 percent of the tungsten market is dominated by one country, the material itself, with a global production of about 80,000 metric tonnes, is not rare enough to be a concern.” And when it comes to cost, a 4-inch tungsten wafer tends to retail for less than $100 dollars – so less than one-tenth of the price of a 2-inch GaN wafer.

To produce their GaN-on-tungsten p-n diodes, the team loaded a 650 µm-thick sapphire substrate into an MOCVD reactor and deposited a 2.2 µm-thick sacrificial layer, followed by a 2.4 µm-thick highly conductive cathode layer and a 10 µm-thick drift layer. Regrowth of p-type layers with a total thickness of 530 nm, and the in-situ activation of the dopants, took place in another MOCVD reactor.

Stealth laser scribing reduced wafer bow from around 300 µm to just 20 µm, prior to defining the mesa structure with lithography and etching, the addition of contacts, passivation, and etching 200 µm trenches around the chips to facilitate early chip singulation.

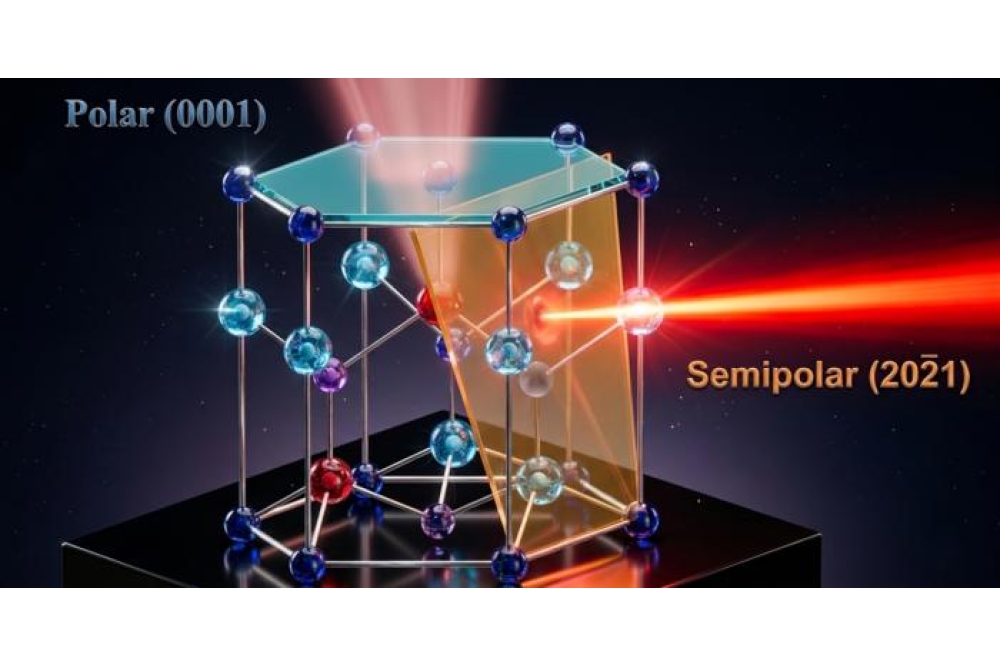

Figure 2. Researchers at Bristol University have compared the electrical characteristics of (a) p-NiO gated HEMT (b) trench MOSFET and (c) MOS-HEMT.

Before laser-lift off, the team polished the backside of its sapphire substrate, slashing roughness from around 1 mm to less than 50 nm to improve the laser lift-off process. After attaching a temporary carrier to the wafer, ultrashort pulses from a 266 nm laser provided GaN decomposition, allowing removal of sapphire, prior to the addition of a tungsten wafer and the extraction of the temporary carrier (see Figure 1).

Thanks to the full conduction path through the tungsten substrate, on-resistance fell after the transfer process from 3.4 mΩ cm-2 to 1.7 mΩ cm-2.

The researchers state that the reverse characteristics are not significantly affected by the transfer process, with only a minor increase in reverse bias current at voltages of more than 400 V. The average breakdown before membrane transfer is 1015 ± 47 V, and after the full process it’s 988 ± 57 V. Following substrate removal and membrane transfer, the reverse bias current at 1000 V increases from around 0.35 mA cm-2 to 0.75 mA cm-2.

Brusaterra says that one of the drawbacks of the team’s process, when it comes to commercialisation, is that it’s a single-wafer process with limited throughput. “Tungsten dicing is also time consuming on large scale.”

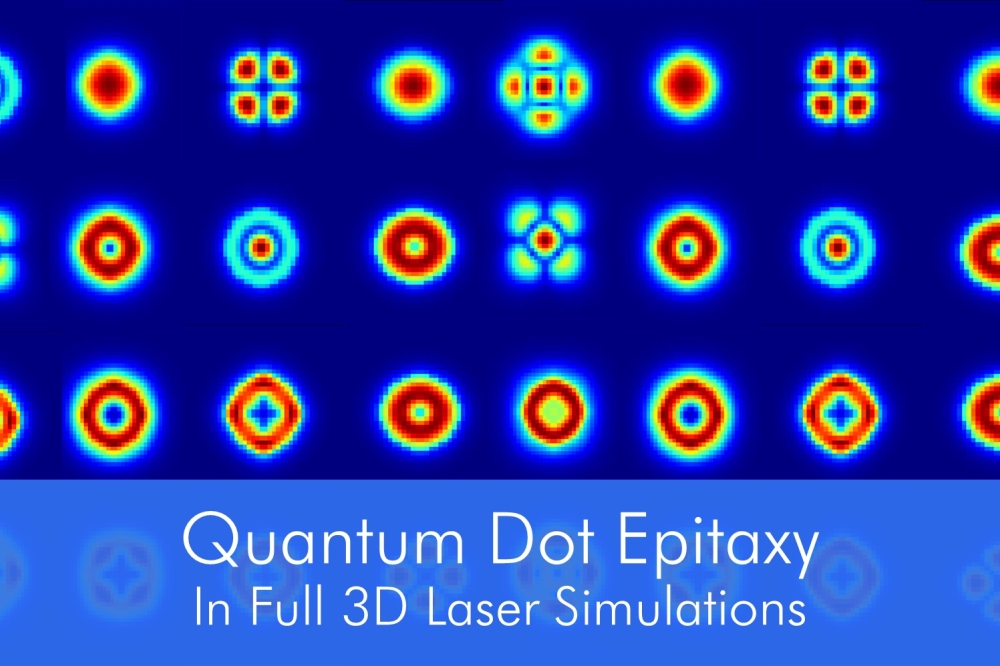

Figure 3.Bristol University’s N-polar AlN/GaN HEMTs with a p-NiO gate show encouraging transfer characteristics.

Giving GaN a NiO gate

Conventional GaN HEMTs, fabricated with growth along the (0001) axis, are described as III-polar devices. This architecture has a number of merits, most notably the creation of a two-dimensional electron gas (2DEG) at the interface of GaN and AlN, thanks to advantageous band offsets and piezoelectric and spontaneous polarisation. But even more favourable are the N-polar structures, realised through growth along the (0001<bar>) direction, that allow AlGaN to act as a back barrier below the GaN channel, and ensure better control of the 2DEG, due to improved carrier confinement. What’s more, with N-polar devices, it’s easier to form an ohmic contact to the 2DEG, there’s enhanced carrier density, thanks to a deeper quantum well, and channel mobility is higher, due to supressed alloy disorder scattering.

Unfortunately, it’s not trivial to enjoy all of these benefits. It is challenging to grow high-quality N-polar GaN on all the common substrates, as compared with III-polar growth, there’s a tendency for higher dislocation densities, greater surface roughness, and increased impurity incorporation. Another issue is that N-polar surfaces are chemically reactive, making interface quality and surface treatment challenging, with threats of traps and instability.

Taking on these challenges – and advancing N-polar HEMTs with GaN/AlN devices that feature the addition of a p-type NiO gate stack that ensures a positive threshold voltage – is a team from Bristol University that detailed their success at this year’s CS Mantech.

Discussing this work with Compound Semiconductor, team spokesman Chengzhi Zhang explained that their device is orientated towards power applications, but it could also be deployed in some RF applications.

According to Zhang, the team’s N-polar GaN/AlN platform enables high 2DEG channel densities, due to strong polarisation fields. “This enables high current and output power densities.”

Thanks to the AlN back barrier, their HEMT benefits from enhanced channel confinement that trims buffer trapping and vertical leakage, and ultimately offers a pathway to solving reliability issues and current collapse. “These are all crucial for power electronics applications,” remarks Zhang.

He points out that the use of a p-type NiOx gate stack layer enhances gate control over the channel and enables normally-off (enhancement-mode) operation, which is very desirable for power switching applications. “The high breakdown field and excellent thermal conductivity of AlN also make it suitable for high-efficiency power conversion.”

The attraction of using NiO is that it’s naturally p-type, with excess oxygen creating Ni3+ vacancies that introduce hole conduction. Due to this, p-NiO is a compelling candidate for replacing p-GaN in HEMT gate stacks. With p-NiO, there’s the promise of a simpler and lower-temperature synthesis process, a higher hole concentration and a work function that’s comparable to p-GaN.

To evaluate their N-polar HEMTs with a p-NiO gate, the team used an N-polar GaN/AlN wafer to co-fabricate these devices, along with trench MOSFETs and MOS-HEMTs (see Figure 2). Fabricating trench MOSFETs from this epiwafer, which features a 460 nm N-polar AlN layer and a 5.4 nm GaN channel, involved using an inductively coupled plasma to etch the GaN channel and part of the AlN layer in selected regions. For all forms of HEMT, electron-beam evaporation provided the ohmic contact. Plasma-enhanced CVD added layers of SiN, and magnetron sputtering with a NiO target added a 30 nm-thick layer of NiO.

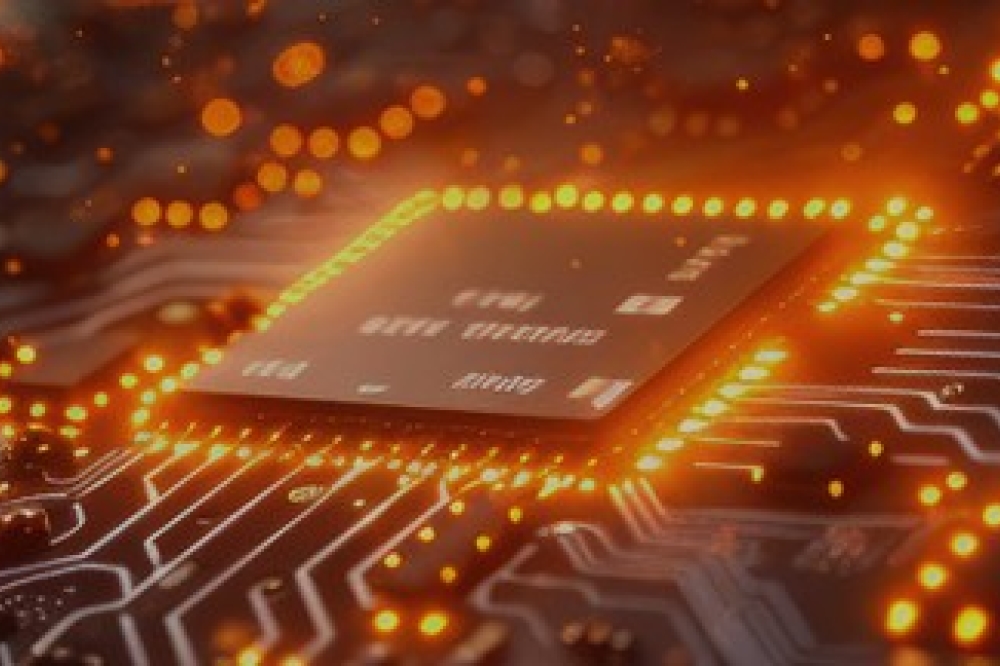

Figure 4. Optical image (top) and a cross-sectional illustration of vertical GaN p-i-n diodes produced and investigated by a team led by the US Naval Research Laboratory, and supported by researchers from the University of Florida, Amentum and Sandia National Laboratories.

Electrical characterisation of all three forms of HEMT have shown that for the MOS-HEMT, it’s not possible to realise pinch-off at even -25 V, despite the close proximity of the gate electrode to the surface 2DEG channel. Note that more negative voltages are prohibited, due to the onset of leakage currents through the gate dielectric. The team have attributed this behaviour to the large conduction band and polarisation offset at the GaN/AlN interface that confines the 2DEG to the channel and impairs depletion. Compounding this issue is the lower conduction band offset between SiN and N-polar GaN that limits the effective voltage range.

With the trench MOSFET, channel current is low over a large voltage range – or, to put it another way, the device fails to turn on. This is attributed to a low background carrier density in the AlN back barrier layer, with the Fermi level remaining below the conduction band and no channel forming.

The transfer curve for the N-polar HEMTs with a p-NiO gate (see Figure 3) shows that p-NiO plays an important role in channel control, with a threshold voltage of +1.24 V. The on-off ratio is 107, the subthreshold swing is 175 mV dec-1, maximum transconductance 18 mS mm-1, and the maximum saturation output current density 50 mA mm-1.

Breakdown measurements reveal that these structures can withstand 0.8-1.0 MV cm-1, leading the team to claim that N-polar GaN/AlN shows strong potential as a material platform for power electronics.

For the N-polar HEMTs with a p-NiO gate, Zhang and co-workers fabricated about 70 devices, with around 50 FETs working normally. “The cause of failure for the remaining devices is still under investigation.”

He says that other goals for the team are to: achieve higher breakdown, by including electric field management techniques adapted from III-polar devices; to optimise growth conditions to achieve higher mobility; and to optimise device fabrication processes, to improve channel mobility and further enhance stability.

3.3 kV planar GaN diodes

Another partnership that is working to improve the performance of high-voltage GaN power devices is that led by the US Naval Research Laboratory, and supported by researchers from the University of Florida, Amentum and Sandia National Laboratories.

This team has been investigating the robustness of vertical devices, which are rapidly maturing, thanks to the widespread availability of 50 mm free-standing GaN substrates and imminent 100 mm availability. However, before these devices can enjoy significant commercial success, there’s a need for detailed investigations of their lifetime and reliability under stress, as the more common lateral structures have very different degradation mechanisms. Studies on vertical studies should include the impact of ion-implanted termination of high-voltage devices, as this relies in impact-induced damage, which may be altered by high operating temperatures or stress.

To help look into these matters, the US collaboration that’s led by the US Naval Research Laboratory has been studying vertical GaN p-i-n diodes, produced by MOCVD on bulk GaN substrates. Using growth rates that are typically around 2 µm hr-1, the team has produced epiwafers with a 25 µm-thick n-type GaN drift layer, a 470 nm-thick p-type GaN layer and a 30 nm-thick heavily doped p-type GaN cap, prior to the formation of terminated devices, using nitrogen implantation at up to 180 eV in a castellated structure (see Figure 4). After adding an anode and blanket cathode with electron-beam evaporation, the team did not apply a contact alloying anneal, with contacts utilised as deposited.

These devices exhibit a differential on-resistance below 5 mΩ cm2 and a breakdown voltage of 3.2-3.4 kV, for 10 A class diodes with a size of around 1 mm2.

To assess the robustness of their devices, the team applied high-temperature reverse-bias testing at more than 80 percent of the breakdown voltage, under vacuum and without passivation or packaging of the diodes. Periodic plots of current as a function of voltage enabled an evaluation of the degradation of the breakdown characteristics.

In addition, the team thermally stressed a cohort of 60 devices under nitrogen, using a rapid thermal anneal of 60 minutes, with sequential testing at increasing temperatures.

The researchers found that their devices exhibit a range of breakdown behaviours. As well as ‘ideal’ behaviour – described as low current leakage at 90 percent of breakdown, and a repeatable sharp breakdown – the team also found that some of its devices showed: a repeated sharp breakdown with significantly elevated leakage; and a ‘soft’ breakdown, with a significantly elevated leakage and a less distinct increase in reverse current density at the breakdown voltage. Devices exhibiting all three forms of breakdown showed avalanche-type behaviour, with reverse electroluminescence uniformly under the anode, or visible at an anode corner spot.

When stressing at 150 °C, a device exhibiting ‘ideal’ behaviour had a consistent low leakage of around 0.5 µA cm-2, up to the end of testing – that’s around 440 hours. However, periodic probing produced a softening of sharp breakdown and a slight reduction in breakdown voltage. This softening started after 88 hours of testing, and at 112 hours the breakdown voltage decreased from around 3350 V to 3275 V, before stabilising. Following 438 hours under 150 °C, and then 84 hours at 200 °C, degradation totalled 6 percent.

Encouragingly, after this high-temperature reverse-bias test, the diode still retained its avalanche-type behaviour. Forward behaviour did not change, and the device still maintained broad emission under the anode, when exhibiting reverse electroluminescence.

During testing of two additional diodes under a high-temperature reverse-bias test at 200 °C, the team observed minimal breakdown degradation or shape change over 408 hours. According to the researchers, this divergent behaviour of the die, despite co-processing on the same wafer, highlights the need for further in-depth study.

Due to the variation in diode behaviour, and the limitation of the testing equipment to 200 °C, the team annealed a cohort of five diodes for 60 minutes in 50 °C steps from 250 °C to 500 °C.

At all temperatures, the diodes remained functional in forward and reverse, but the breakdown voltage diminished, and softened markedly after stressing at 350 °C.

According to the team, the change in reverse-bias behaviour through thermal stress indicates changes to the termination structure. It is suggested that as the hybrid termination structure makes use of nitrogen implantation and the resultant damage, long-term stability of the diode may be governed by the diffusion of point defects, or the annihilation of Frenkel pairs.

The lead author of the CS Mantech paper detailing this work, Alan Jacobs, told Compound Semiconductor that the team continues to investigate these devices, but with less time/effort, given the programme that funded this work has completed.

“That said, the devices that are divergent are still viable, and we plan on doing further electroluminescence imaging and cathodoluminescence imaging to see if the termination structure has changed due to thermal stressing. Tracking these changes and how they modify the field distribution would improve our ability to design a more robust termination structure, and also investigate mitigation techniques for a more temperature-agnostic design.”

Ga2O3 superjunction structures

In recent years, the ultra-wide bandgap material Ga2O3 has started to feature at CS Mantech. This oxide is attracting much attention, because it promises to enable the production of devices with incredibly low losses and a high electrical breakdown field. However, progress is held back by a lack of p-type doping, preventing the fabrication of p-n junctions.

To sidestep this issue and produce enhancement-mode transistors that don’t require p-type doping, a number of different device architectures have been proposed, including finFETs. Laying the foundations for producing such devices, via simulations and etching development, is a team led by Swansea University, which has just commissioned an Aixtron close-coupled showerhead deposition system that’s capable of the growth of 4-inch Ga2O3-based epiwafers.

Lead-author of the CS Mantech paper detailing the simulations and etching work, Swansea University’s Nicholas Edwards, told Compound Semiconductor that team’s calculations, using the Silvaco framework, outline the blueprint for realising high-breakdown, enhancement-mode devices, while also revealing the underlying operation mechanism.

One of the challenges when try to simulate the performance of Ga2O3 devices is a lack of consensus concerning carrier mobility models.

“It is difficult to get consensus on monoclinic crystal structures such as beta gallium oxide, due to a lack of symmetry,” says Edwards, who points out that with any next-generation material, discrepancies will exist among the available models.

“The models we implemented are based on literature and validated through experimental results, making them the most accurate to date. While absolute values may vary slightly, the key findings and design insights remain consistent and reliable.”

The team’s simulations show that it’s possible to produce enhancement-mode β-Ga2O3 finFETs with a 5 kV blocking voltage using a doping concentration below 1016 cm-3 and fins with either: a width of 200 nm and a thickness of 0.8 µm; a width of 400 nm and a thickness of more than 1.2 µm; or a width of 600 nm and a thickness of more than 2 µm.

Also involved in this collaboration is KLA, another key player in the compound semiconductor cluster in South Wales.

The SPST SyapseEtch module made by KLA has been used in this investigation to etch β-Ga2O3, due to its high plasma density that facilitates the etching of materials with strong chemical bonds.

Using a 1 µm-thick SiN hard mask, deposited using an SPTS plasma-enhanced CVD module, the team have identified that there is a wide process window for the etching of β-Ga2O3.

Adjusting the applied power, which alters the etch rate, does not influence the vertical sidewall profile – this remains highly vertical, with an angle of 88°. However, the lower etch rate produces a flat trench base with rounded corners, viewed as potentially advantageous for finFET mesa fabrication, while the faster edge rate appears better-suited to edge-termination structures requiring deeper etches.

According to Mike Jennings from the Centre for Integrated Materials (CSIM) at Swansea University, work on the development of Ga2O3 will continue.

“This [etching] process has now been successfully transferred to the CISM fabrication facility. The next phase involves device fabrication and performance characterisation.”

Such efforts will help to advance the prospects of Ga2O3 devices, which are likely to feature, along with their GaN and SiC cousins, at next year’s CS Mantech – it will be held in Portland, Oregon, in mid-May.