Cubic SiC: Tomorrow’s champion for power electronics?

Offering the same crystal structure as silicon, alongside a

wider bandgap and the potential for high reliability, what’s to stop

cubic SiC from playing a major role in tomorrow’s power electronics

industry?.

BY MIKE JENNINGS FROM SWANSEA UNIVERSITY

The uptake of the Tesla is welcome on many fronts. Its lack of a combustion engine helps to trim carbon emissions; it is relatively quiet, thanks to battery power; and, much closer to home for those within the compound semiconductor industry, its early adoption of SiC power electronics is driving sales of these devices.

Where Tesla leads, other makers of electric vehicles are sure to follow. They too will employ SiC devices in their power trains, swelling sales of these wide-bandgap devices. Demand is tipped to be so strong that four of the leading makers of these chips – Wolfspeed, Infineon, STMicroelectronics and onsemi – are forecasting annual sales from this class of device to top $1 billion by the middle of this decade. Given the phenomenal success that SiC power devices are set to enjoy, one would presume that they are free from flaws. But that’s not actually the case. There are, in fact, significant concerns relating to reliability, centred around the gate oxide.

The predominant role that SiC power devices have in electric vehicles is to convert the output from the battery, which is typically 800 V DC, to an AC form that drives a motor – producing up to 200 kW or so of power. The voltage requirement is not particularly testing, as its well within the range of most conventional 4H-SiC devices, which span 650 V to 1.7 kV.

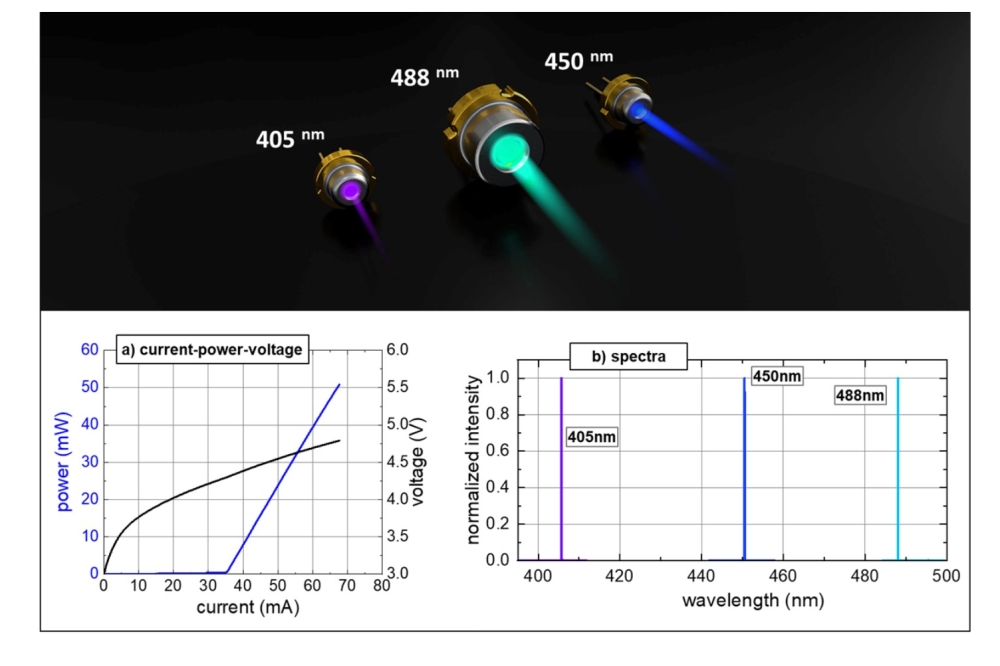

Figure 1: Electrical and material properties radar chart of cubic SiC

versus silicon and other commercial wide bandgap materials. This chart

presents major semiconductor material parameters for power electronics

applications.

There are concerns surrounding the gate oxide because, like its silicon counterparts, the 4H-SiC transistor is based on a vertical MOSFET design. With this architecture failure of the gate oxide at elevated temperatures is a primary weakness. This is not that surprising, as the gate oxide used in this form of MOSFET is much thinner than its silicon equivalent, in order to maintain an acceptably low threshold voltage. Unfortunately, two unwanted consequences result from this thinner oxide: increased importance of the oxide-semiconductor interface, and an electric field inherent within the oxide that is typically two-and-a-half times that at the SiC surface.

Both these issues are particularly troublesome in trench MOSFET architectures, because they are exacerbated by the trench corner. To counter this, those designing the latest trench MOSFET devices derate their blocking voltage capability to protect the fragile gate oxide.

Another option for addressing concerns related to reliability is to mirror the approach that’s taken with GaN devices. Taking this tact has led some designers to advocate cascode co-packaged devices, such as the pairing of a 4H-SiC JFET with a silicon MOSFET. But this combination constrains performance, particularly at high temperatures.

Cubic SiC: a bastion for longevity

Enter cubic SiC, also known as 3C-SiC – an exciting material that promises to be ‘Mr Reliable’! There’s still much work to do with this polytype, as wafers and epitaxial layers are at a very early stage and hence, defective. However, massive strides in bulk material and the growth of 3C-SiC on silicon have been recently accomplished – they are detailed in the previous edition of this magazine by Francesco La Via from the Institute of Microelectronics and Microsystems at Catania, Italy.

You may be wondering why so much excitement surrounds 3C-SiC. After all, compared with GaN and 4H-SiC it has a lower bandgap, a smaller critical electric field, a modest electron mobility and a low thermal conductivity (see Figure 1). Surely, this shows that 3C-SiC is inferior to those two wide bandgap titans, GaN and 4H-SiC. While all of these pointers are valid, they overlook two crucial factors

that are not covered within tables listing the properties of

semiconducting materials: processing, including the quality of the

interface, which may involve a metal or insulator; and reliability in

the field. These are considerations that clearly matter. After all, what

good is a wide bandgap material if it cannot be used to make a device,

or one that only lasts for a single switching cycle.

Figure 2: Interface trap density plot comparing cubic (3C-) SiC to

commercial (4H-) SiC. 3C-SiC shows a favourable (or much reduced) trap

density due to the absence of near-interface traps prevalent within the

4H- system. This is a plot is modified from R. Esteve, “Fabrication and

Characterization of 3C- and 4H-SiC MOSFETs,” Doctoral thesis, KTH Royal

Institute of Technology, Stockholm, 2011.

Of course, these concerns don’t apply to commercial 4H-SiC and GaN – but processing of these materials, particularly GaN, is radically different and more challenging than it is for traditional silicon. In comparison, 3C-SiC, with its cubic nature and a humble energy bandgap of 2.36 eV, is closer to silicon than the other members of the wide bandgap family. These traits offer many benefits when it comes to processing 3C-SiC into devices.

Let’s first consider the MOS interface. Power electronics applications engineers tend to want a high impedance gate, such as a MOS gate. That’s proved elusive to the developers of 4H-SiC devices, who have been grappling with a poor MOS interface for the best part of 30 years – even today, it is still its Achilles heel. In the early days of the 4H-SiC MOSFET, inversion mobility was so poor – typically just 5 cm2 V-1 s-1 – that the channel resistance constituted more than 90 percent of total device resistance. This is unacceptably high and untenable, in terms of utilisation within a power electronics converter. While poor mobility in 4H-SiC is now managed, as alluded to earlier, there are still problems associated with the move to trench architectures, centred around high-temperature reliability issues.

There are three main types of trap adversely affecting the MOS interface: near-interface traps; acceptor-like carbon clusters; and dangling bonds, which occur at the interface (see Figure 2 for an illustration of trap types, and a comparison of the 4H-SiC and 3C-SiC MOS interface). With 4H-SiC, the conduction band edge is swamped by all types of trapping mechanisms, including near-interface traps, which are the most dominant. In stark contrast, 3C-SiC is not affected by these near-interface traps. Of course, it is still hampered by acceptor-like carbon clusters, which have a far greater impact than dangling bonds. One key consequence of these three forms of trap is that alternative approaches to hydrogen annealing are typically required to passivate the SiC MOS interface.

What is the important takeaway from all these considerations? It’s that far less effort should be required to realise higher channel mobilities, and thus lower on-state resistances, when it comes to 3C-SiC MOSFETs. In fact, efforts at developing 3C-SiC MOSFETs are already bearing fruit, with mobilities of more than 100 cm2 V-1 s-1 demonstrated.

It is worth noting that in addition to these results for 3C-SiC-on-silicon, there is work with bulk 3C-SiC that indicates improved performance and commercial viability for p-n diodes. Potential merits of bulk 3C-SiC, as opposed to the heteroepitaxy of 3C-SiC on silicon, include ease of processing technology with respect to ion implantation and metallisation. There is also the promise of scaling the voltage through adjustments to layer thickness, an attractive attribute from a commercial standpoint. This feature is especially welcome at voltages beyond 650 V, where there is competition from silicon MOSFETs, superjunction devices, insulated gate bipolar transistors, 4H-SiC MOSFETs and GaN HEMT topologies.

At Swansea University, our team is working to prove these new materials for automotive applications. The automotive and aerospace industries are notorious for insisting upon the highest reliability standards whilst keeping the cost to a minimum. That means testing gate oxides to high temperatures and performing accelerated lifetime analysis at the chip-level. Physical considerations suggest that 3C-SiC could offer excellent reliability. Its band offset to the SiO2 gate oxide is 3.7 eV, a value much larger than that for silicon and 4H-SiC (see Figure 3). This is a major asset, as for a given critical electric field for the dielectric, the tunnelling current through this oxide is exponentially dependant on the band offset, which is sometimes referred to as the barrier height. One consequence of this advantage is that the electric field within a 3C-SiC MOS system can be two-to-three times higher than that for 4H-SiC, for the same leakage current into the gate driver circuitry. Due to this, de-rating requirements for a 3C-SiC trench power MOSFET can be far less stringent than those for a 4H-SiC sibling.

Figure 3: Semiconductor-SiO2 band offsets of other wide bandgap

materials compared to cubic (3C) SiC, taken from F. Li et al. Materials

14 (2021)

The 3C-SiC MOS interface also promises a high level of gate oxide reliability and a long lifetime. Measurements by Swansea University in collaboration with Warwick University on a structure with an interface formed with a gate oxidation process based on N2O show a stabilised leakage current and a critical electric field strength at around 8 MV/cm, which is the highest value observed for a 3C-SiC MOS structure. Even preliminary 3C-SiC MOS capacitors, formed on epitaxial material with an inherent high defect density, offer a breakdown field strength of 8 MV/cm, approaching values for 4H-SiC of typically 9 - 11 MV/cm.

Our team has recently carried out a time-dependent dielectric breakdown analysis of 3C-SiC MOS capacitors (see Figure 4). We attribute their low failures to crystal deficiencies in the 3C-SiC substrate that have an impact on the localised material properties. For high field failures – that’s a field strength of more than 8.5 MV/cm – failures result from an increased leakage current, or impact ionisation, due to high critical electric fields.

Figure 4: Distribution of failures of 3C-SiC MOS capacitors for varying

electric fields (a) and corresponding Weibull distributions (b), taken

from F. Li et al. Materials 14 (2021). The time dependent dielectric

breakdown analysis is conducted at electric field values of 6 - 9 MV

cm-1. The failure percentage increases steadily up to an electric field

strength of 8.5 MV cm-1, above which, the failure number rapidly

increases to 100 percent.

The primary conclusion from this work is that even at high electric fields, exceeding 8.5 MV/cm, acceleration slopes remain low for 3C-SiC. These slopes are an order of magnitude lower than 4H-SiC, suggesting extrinsic defects are still the dominant failure mechanism overall.

Further reading

⊕ F. Blaabjerg and S. Round. “Power Electronics: Revolutionizing the world’s future energy systems” https://www.hitachienergy.com/uk-ie/en/news/perspectives/2021/08/power-electronics-revolutionizing-the-world-s-future-energy-systems.

⊕“Automotive Council UK and Advanced Propulsion Centre UK Roadmap 2020 Power Electronics,” https://www.apcuk.co.uk/app/uploads/2021/09/https___www.apcuk_.co_.uk_app_uploads_2020_11_Technology-Roadmap-Power Electronics.pdf.

⊕ F. Iannuzzo. “Reliability Challenges of Automotive-grade Silicon Carbide Power MOSFETs,” https://eepower.com/technical-articles/reliability-challenges-of-automotive-grade-silicon-carbide-power-mosfets/#.

⊕ J. O. Gonzalez et al. “Performance and Reliability Review of 650 V and 900 V Silicon and SiC Devices: MOSFETs, Cascode JFETs and IGBTs,” IEEE Trans. Ind. Electron. 67 7375 (2020)

⊕ F. Li et al. “Status and Prospects of Cubic Silicon Carbide Power Electronics Device Technology,” Materials 14 (2021)