Targeting the C-band with ultra-high-voltage HEMTs

GaN HEMTs with a minimal output capacitance and terminated harmonics deliver record-breaking powers and efficiencies.

BY SEBASTIAN KRAUSE FROM THE FRAUNHOFER INSTITUTE FOR APPLIED SOLID STATE PHYSICS IAF

During the last decade the GaN-on-SiC material system has established itself as the dominating semiconductor technology for delivering very high powers in the gigahertz range. Its more established rival, silicon-LDMOS, is more popular, and the cheaper choice for powering most systems in the VHF and lower UHF spectrum. However, this incumbent is even losing market share in that application space to GaN: this wide bandgap rival is renowned for its higher device efficiency, which trims operational expenses; and its higher power per die area that enables the design of smaller and lighter systems.

The enviable position that GaN holds in the high-power market is primarily due to its capability to maintain a high efficiency, even at high voltages and hence high-power levels. In contrast, LDMOS struggles to find a sweet spot that ensures a good efficiency, alongside a high-power density and high-frequency performance. So usually a trade-off has to be made in device design, favouring one attribute. Or, to put it another way, GaN has the stamina to go the extra mile, in terms of its frequency range, while LDMOS is already running out of gas.

However, there’s a need to understanding the underlying physical principles of these limitations, and pinpoint the critical device parameters that require careful tuning, in order to optimise GaN devices. Clearly, device scaling does not come for free.

Figure 1. Drain-Source breakdown characteristics for a device with a

total gate width of 1.2 mm (6 x 200 µm). For the measurement, the source

of the device is grounded, whereas the gate potential is set to - 10 V.

Then the drain potential is quickly raised until the recorded gate and

drain current exceed the compliance value of 1 mA/mm, which is

considered as breakdown.

Looking towards higher frequencies, the predominance of GaN is built on its capability to deliver very high powers and efficiencies. Yet, generally accepted scaling rules apply, implying that operation at higher frequencies must go hand-in-hand with a reduction in supply voltage. Consistent with this expectation are the product portfolios of manufacturers: they list the availability of 65 V devices up to 2 GHz, while those capable of 12 GHz and 18 GHz seem to mark the final frontier for 50 V and 40 V transistors, respectively. Beyond that, devices are rated for 28 V operation, if at all.

Last summer Integra Technologies of El Segundo, CA, launched a packaged 100 V GaN HEMT. This product pushes the boundaries for the supply voltage and ultimately the output-power-per-device. Designed for L-band avionics radar operating in the 1.030 GHz to 1.090 GHz band, this HEMT adheres to the mapped-out trend, highlighting once again that higher frequencies must be traded for supply voltage.

There are applications demanding kW-level powers higher in the spectrum, such as the C-band (4 GHz to 8 GHz) and even the X-band (8 GHz to 12 GHz). It makes much sense to try and address these opportunities with GaN, by taking on the challenge of marrying its high-frequency attributes with its outstanding high-power capabilities.

Keeping control of the charge

Unfortunately, when designers move to higher voltages, there is not much working in their favour. In fact, almost every critical performance parameter appears to get worse when raising the supply – there are problems associated with the transition frequency, greater trapping and diminished reliability to name but a few. All these issues stem from the rising electric field, which is the main factor to consider when trying to maintain performance when shifting operation to higher voltages.

Another major downside of a higher electric field is that it can lead to so-called ‘short-channel effects’. When this happens the gate, which is solely responsible for controlling the electrons in the channel under ideal conditions, struggles to do its job. Short-channel effects tend to be associated with high-frequency technologies, because their occurrence usually leads to an ‘under scaling’ of electrical parameters – that is, electrical parameters scale less than what the scaling rules imply. Note that broadly speaking, scaling up in frequency or in voltage leads to similar field-related issues, unless appropriate countermeasures are taken.

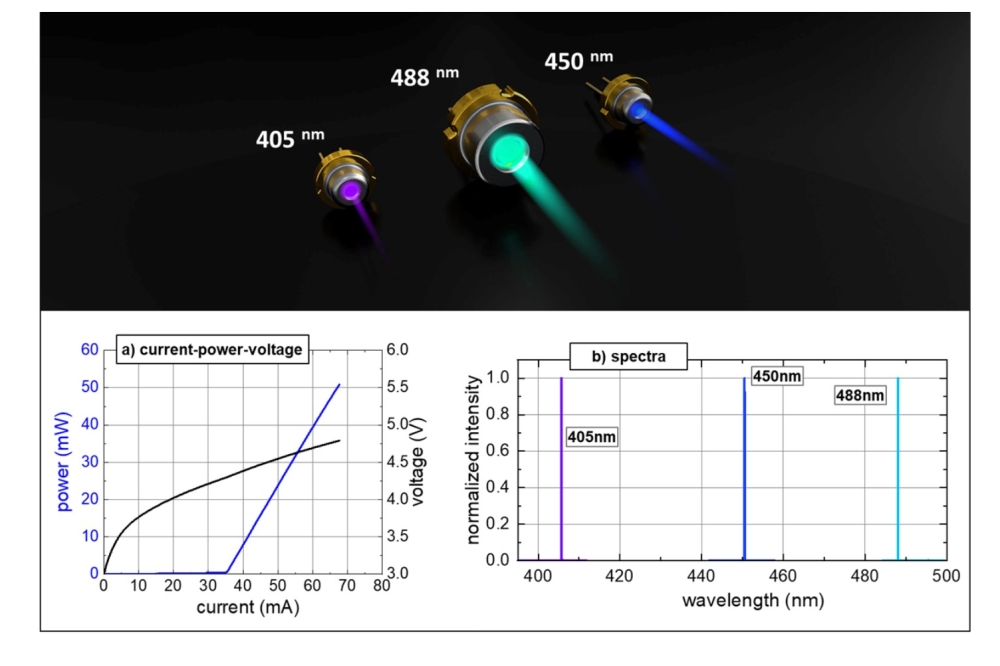

Figure 2. Pulsed load-pull measurements of a 100 V GaN HEMT with a total

gate width of 2.4 mm (6 x 400 µm) at 2.0 GHz. The pulse width is 100 µs

with a duty cycle of 10 percent. Two conditions are plotted here.

Orange is for load pull at the fundamental frequency without termination

of harmonics, while blue is for fundamental load pull with second

harmonic impedances at input and output set for maximum efficiency.

One common countermeasure is to introduce field plates, a concept found in most GaN technologies up to Ka band. As its name suggests, the role of the field plate is to tame the electrical field by spreading this out from the gate towards the drain electrode. With its addition, there is a reduction in the maximum electric field close to the gate contact, and a quashing of short-channel effects. Another benefit is that a device can realise a higher breakdown voltage for a given on-resistance. Since a higher on-resistance translates to increased losses, it is crucial to keep this as low as possible when targeting the highest efficiency. Working at the Fraunhofer Institute for Applied Solid State Physics IAF, our team is engineering devices to try and meet these criteria. Measurements show that the breakdown voltage for our 100 V GaN HEMTs is in excess of 350 V (see Figure 1). Meanwhile, on-resistance is just 4.2 Ω mm, a value merely one-third higher than that of established 50 V GaN processes.

Setting the stage for harmonics

At first glance, it would appear to be rather conservative to have such a high breakdown voltage for a 100 V device. However, there is good reason behind this caution – harmonic termination. When you dive a bit deeper into high-efficiency amplifier design, you are very likely to come across this technique of manipulating harmonic impedances.

Ultimately limiting the efficiency of an ideal amplifier is its class of operation. While class A and class B are probably familiar to most of us, brave designers opt for class E, class F or class F-1, which is also known as inverse class F. These latter three have a theoretical efficiency of 100 percent, while class B and class A are limited to 78.5 percent and 50 percent, respectively. In practice, all these numbers are impossible to achieve, due to the lossy nature of real devices. However, efficiencies as high as 90 percent have been demonstrated for GaN HEMTs. I doubt you expected a free lunch, so you’ll not be surprised that harmonic termination comes at a cost. Presenting specific impedances to the device at its harmonic frequencies – ideally a short or open circuit – alters the time domain waveform at the device output. For Class E and class F-1, there can be waveforms with a voltage magnitude as high as three-and-a-half times the supply voltage. Such a high voltage arises due to the high second harmonic impedance (at or close to an open circuit) that is required for the operation modes. Due to this, a sufficiently high breakdown voltage is a pre-requisite for reaching the highest efficiency levels.

At higher frequencies the concept of harmonic termination slowly falls apart. This arises because real devices show a finite output capacitance in parallel to the intrinsic current source. Over frequency the reactance of the output capacitance decreases, forming a shunt current path to ground. If the designer now tries to force the device into class-E or class-F-1 operation, the open circuit at the second harmonic is bypassed by the output capacitance. At a certain frequency this results in an effective short-circuit for the second harmonic and all higher harmonics. This set of shorted harmonic impedances leads to the class-B condition, limiting the maximum theoretical efficiency from 100 percent to 78.5 percent.

In addition to this road block to realizing a high efficiency at high frequencies, there is another issue associated with high voltages. In this case it is the praised field plates that are part of the problem. Most troublesome are the so-called source-terminated field plates – they can account for a large proportion of a device’s output capacitance. It’s tempting to simply ban this form of field plate from the device layout, but such a move would contradict the goal of proper field control. Like many times in life, it’s better to seek a good trade off.

Figure 3. Pulsed load-pull measurements of a 100 V GaN HEMT with a total

gate width of 0.9 mm (6x150 µm) at 7.2 GHz. The pulse width is 100 µs,

with a duty cycle of 10 percent. No harmonics have been terminated

during the measurement.

Stepping up in efficiency

Previously, we demonstrated a power-added efficiency of more than 77 percent at 1.0 GHz, a record for 100 V GaN HEMTs at the time. However, we uncovered some weak spots when we compared this device to our baseline 50 V devices. Deficiencies included a maximum efficiency that lagged the baseline devices by around 7 percentage points. We also observed a pronounced efficiency roll off when measuring our 100 V devices at higher frequencies.

To address these weaknesses, we decided to make a fresh start. This involved redesigning the epitaxial stack and the intrinsic device features, with the goal of tightening the electrostatics. When we extracted the drain-induced barrier lowering – a measure that quantifies the parasitic control over the electrons by the drain contact, with the lower the value the better – we verified our success. This key figure of merit showed a five-fold reduction, yielding a value below 1 mV/V. In a nutshell, this result reveals that the gate has all the power over the electrons, without any interference from the drain at high voltages.

Further measurements underscored the capability of this new device. They revealed a record-breaking power-added efficiency for our 100 V GaN HEMT at 2.0 GHz of 84.7 percent – that’s an increase of almost 8 percentage points, despite a doubling in frequency. The maximum power density hit 15.5 W/mm (see Figure 2).

There’s more to our second-generation device than just headline-grabbing figures. By revising the intrinsic device layout, we have shaved off as much of the output capacitance as possible without deteriorating electrostatics. This refinement should enable these transistors to operate efficiently at much higher frequencies than before. By trimming the output capacitance by 40 percent, theory would suggest that these devices are susceptible to harmonic termination at higher frequencies.

Evidence from the lab supports this view. Measurements at the upper C-band frequency of 7.2 GHz – used by the European Space Agency for Deep Space Antennas to track spacecraft throughout the complete solar system – provide very impressive results. According to fundamental load-pull measurements, the power density is only a little down from the value for 2.0 GHz, reaching an impressive 13.8 W/mm. Meanwhile, power-added efficiency tops out at 57.2 percent.

Still, the question remained on whether terminating harmonic impedances would enhance efficiency. Due to set-up limitations, we could not tune the input and output simultaneously, as we had done for the 2.0 GHz measurement. So we tuned just the output second harmonic, and selected a fundamental load that provided a judicious combination of efficiency and power density. We then optimized the second harmonic phase, until we found the setting that yielded the maximum efficiency (see Figure 4 for the results of the power sweep).

Figure 4. Pulsed load-pull measurements of a 100 V GaN HEMT with a total

gate width of 0.9 mm (6 x 150 µm) at 7.2 GHz. The pulse width is 100 µs, with a duty cycle of 10 percent. For this measurement a ‘trade-off’

of fundamental impedance was chosen that yielded a good combination of

efficiency and power density. Additionally, the second harmonic at the

output of the device was set for the value that showed the highest

power-added efficiency.

The reduction in the output capacitance has paid off. The power-added efficiency has climbed to 66.0 percent, an increase of around 9 percentage points compared with the load pull without second harmonic termination. This value also sets a new benchmark for the efficiency of 100 V GaN HEMTs in the C-band. No less impressive are the associated power density of 10 W/mm and the gain of 18.5 dB, both achieved at the maximum power-added efficiency. Crucially, these performance numbers are realized simultaneously, rather than marking the individually best obtainable values – that sets these 100 V devices apart from commercially available GaN technologies. While the power-added efficiency of our ground-breaking HEMTs is comparable to the best 40 V and 50 V technologies, the power density and gain of our 100 V devices is a big step up from the capabilities of today’s commercially available GaN HEMTs.

We believe that more is possible. There is no reason to think that the C-band is the ultimate limit for 100 V GaN HEMTs. Our high levels of performance at these frequencies imply that there is still room to push the technology towards the X-band. We don’t know where exactly the frequency limitations of these high-voltage devices are, but we are prepared and willing to find out.

Further reading

† S. Krause et al. “100-V GaN HEMT Technology with Record- High Efficiency at C-Band Frequencies,” International Conference on Compound Semiconductor Manufacturing Technology (CS MANTECH), Monterey, CA, USA, 2022

† S. Krause et al. “High-Power-Density AlGaN/GaN Technology for 100-V Operation at L-Band Frequencies,” 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2019, pp. 17.4.1-17.4.4