Tackling the foot

A two-paced deposition process offers the best compromise for forming a metal gate in a high-throughput GaAs fab.

BY KEZIA CHENG AND GUOLIANG ZHOU FROM SKYWORKS SOLUTIONS.

The recent chip shortage has piled immense pressure on foundries looking to increase their production via a boost in throughput and a trimming of cycle time. For those that work there, ramping production is certainly not unchartered territory. However, that does not imply that succeeding is trivial. For example, in GaAs fabs that produce a key component for mobile phones, metallization is often a bottleneck, with wafer yield impacted by a very common yet seldom discussed defect: gold foot diffusion. This issue is so widespread that it can account for up to 40 percent of yield loss.

In these GaAs fabs, a common approach to increasing the deposition rate for metallisation – and ultimately realising a higher wafer throughput – is to add a crucible liner to the evaporation tool. The logic behind this fix is straightforward: Doubling the deposition rate halves the process time and hikes the number of wafers produced per shift. However, cranking up the rate that gold is deposited has its downsides, such as an increase in the likelihood of gold spitting and premature gun failure. To address these concerns, some fabs add tantalum pellets to the crucible liner during gold evaporation. The tantalum ‘getters’ the carbon in the molten gold, thereby tackling the primary reason for metal spitting. A benefit of the crucible liner is that it thermally isolates the gold from the hearth cooling water, ensuring a high deposition rate at a fraction of the normal power.

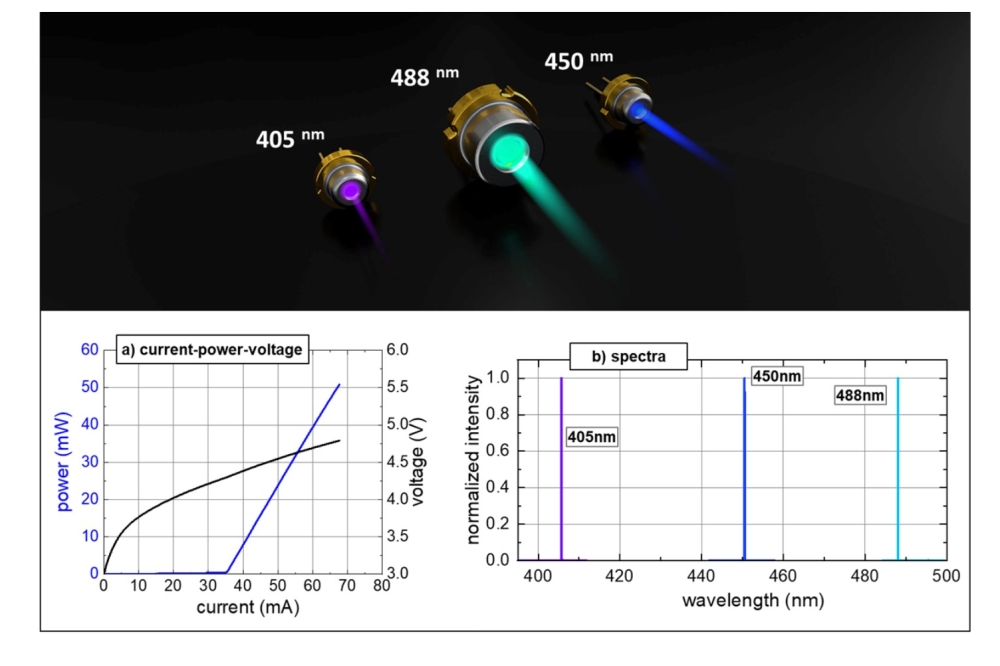

Figure 1. Scanning electron microscopy of a metal line shows the typical

columnar growth and a metal foot, which is a characteristic feature of

lift-off evaporation. If the gold overlaps titanium, it will be a

reliability concern.

The combination of the crucible liner and tantalum ‘getters’ looks like a win-win: the deposition rate increases while reducing gold spitting. But under the eagle eye of a scanning electron microscope a concern arises, as a foot may be seen on the edge of the metal lines after lift-off. While it may be tempting to dismiss this issue, arguing that this little foot looks like nothing, the reality is that this feature can severely impact yields. Up until now, there hasn’t been much exploration into this issue – but before every GaAs microelectronic fab starts to add crucible liners to its evaporators, there’s a need to look closely at the effects on device performance.

Picking up where we left off

Our team at Skyworks has been pondering these issues for many years. Back in 2007 we published an article in this magazine entitled Palladium barrier cuts materials bill (September 2007, p. 19), describing a study of GaAs pHEMT fabrication that identified that the combination of high deposition rates and a beam sweep produced a pronounced foot at the base of the gate electrodes. We were concerned by this, because our process allowed palladium and gold to contact the semiconductor – and threaten, when sufficient activation available, the diffusion of these elements into the epilayer to create current leakage paths.

Figure 2. Gold diffusion at the edge of base metal contact.

To avoid this detrimental occurrence, we reduced our deposition rates for gold and palladium, and applied a beam sweep and a high deposition rate for only the titanium layer. With these modifications, we minimised the gold and palladium overlap with titanium at the base of the gate metal.

One of the key conclusions from that study was that if we could learn how to reduce this foot, we could benefit from higher yields and make an even stronger case for a palladium-based barrier. At that time, we were also exploring how the sticking coefficients of the metals play a role in foot formation – this effect can also have a negative impact on wafer yield.

Fifteen years on, we have conducted experiments that build on our previous study and help us to improve wafer yield further, by also looking at the use of crucible liners for gold evaporation. These recent investigations reveal that a high gold deposition rate, a crucible liner, and a beam sweep all contribute to an exaggerated foot and gate leakage in a pHEMT – and ultimately contribute to device failure. Here, we’ll discuss the results of our experiments to study the gate foot, and our findings on how the size of the foot corresponds to the deposition condition. In addition, we’ll detail our proposed solution.

Gate foot formation: the thorn in our side

The primary metallisation process for fabricating compound semiconductor devices is electron-beam evaporation and lift-off. This begins by placing wafers in high vacuum, prior to deposition with line-of-sight characteristics, thanks to a long mean-free-path and minimal scattering. As previously mentioned, the scrutiny of an electron microscope reveals that this process is imperfect, as a foot may be seen on the edges of metal lines, where a very thin layer of metal extends from the main body beyond the photoresist-defined critical dimension. Note that the physics of foot formation is closely related to metal fencing formation.

There are several stumbling blocks to minimising or eliminating the metal foot. For example, if gold overlaps the underlying titanium, it might diffuse into the channel during downstream processing, causing a high leakage pHEMT. This issue is not limited to the pHEMT, with the presence of a foot in a metal contact causing a similar leakage problem in HBTs.

Several approaches have been tried to reduce the size of the gold foot, including doubling the thickness of titanium and reducing the thickness of gold. However, none have succeeded in trimming either the gold foot or the leakage current.

Figure 3. The wafer clip leaves a shadow on the back of the wafer dome,

providing clear evidence of gold re-evaporation due to a low sticking

coefficient.

The role of deposition

High deposition rates are attractive in fabs, as they can unlock an increase in throughput. For evaporators to provide a high deposition rate, they must be driven at high powers. In this regime there’s an increase in the molten area, with gold atoms sent into a flurry, causing them to collide more frequently. Due to this greater scattering, the spread of the flux-arrival-angle increases, amplifying the presence of the metal foot –which, as we’ve said before, is the bane of our existence.

Another consequence of turning to high deposition rates and elevated evaporation temperatures is that it leads to higher thermal radiation, with heat transferred from the gold source to the shields inside the chamber. Due to this, areas with a lower sticking coefficient are more likely to experience gold re-evaporation. We have observed this, with gold deposition clearly visible on the back of the wafer dome, attributed to gold re-evaporation from surfaces with a low gold sticking coefficient (see Figure 3, which shows a wafer clip masking the reflected gold atoms and leaving its outline on the dome surface).

The re-deposition of gold from nearby structures is more likely when there’s a poor sticking coefficient. This has to be considered when forming gate electrodes, because re-deposition is a factor early in the process of deposition, and can determine the appearance and the size of the metal foot.

As well as considering this, it’s also important to account for: the reflection of gold atoms off chamber walls and shields, and even the gate photoresist (see Figure 4); and increases in scattering and flux angle variation, associated with a crucible liner.

Figure 4. High evaporation rates cause collision between atoms.

Scattering changes the arrival angle that contributes to metal foot

formation early in the deposition process.

We have carried out a number of experiments to determine the influence of the crucible liner. Our key findings are that:

⊕ pHEMTs with the lowest leakage come from wafers produced with a low gold deposition rate, in evaporators without a crucible liner

⊕ using a high deposition rate, but no crucible liner, leads to a more-than-doubling of the pHEMT leakage current

⊕ introducing a crucible liner increases leakage current more than twice. The high leakage accounts for a yield loss of 40 percent

⊕ the combined effects of a beam sweep and a high deposition rate double the circuit leakage

⊕ compared with pHEMTs produced using no crucible liner and a low deposition rate, those fabricated with a high deposition rate in an evaporator with a crucible liner have five times the leakage current

These conclusions may lead you to wonder why the addition of a crucible liner is so deleterious to pHEMT performance. Part of the reason is that in its absence, the gold source in a copper hearth can be completely transformed from solid to liquid, so long as this source is clean and the beam properly adjusted. Due to the contact between the molten gold and copper hearth, there is a steep temperature gradient from the centre of this metallic source to its edge. The gold that’s in contact with the copper hearth maintains a lower temperature, causing evaporation to primarily take place in the centre of this source, where the beam strikes. Thanks to this state of affairs, gold deposition from evaporators without a crucible liner resembles that of a virtual point source.

Figure 5. A gate electrode produced with a high deposition rate for gold

has pronounced foot and gold diffusion (left). Meanwhile, a gate

electrode formed with low deposition rate and no beam sweep has a

minimal gate foot and no diffusion (right).

That’s not the case when a crucible liner is included. Its addition leads to thermal isolation of the source from the water-cooled hearth, and completely molten gold, even at low power. As gold is a good thermal conductor, the temperature of the molten source tends to stay uniform across the entire surface. Adding to concerns, the beam sweep keeps the source molten where the beam passes. Due to this situation, when a beam sweep is applied during deposition, its impact is similar to a source-to-substrate misalignment.

The takeaway from our cumulative experimentation is that contrary to popular practice, a high deposition rate and the use of a crucible liner are detrimental to overall wafer yield. Cranking up the deposition rate and adding a liner leads to an increase in the highly undesirable gate foot, and a higher proportion of unacceptable devices.

Figure 6. A film deposited on the photoresist closes the opening.

Increasing film thickness inside the photoresist opening limits the

number of atoms that can reach the foot to a narrow angle.

Figure 7. A crucible liner has effects similar to source-to-substrate misalignment.

Our solution: ramping up

Increases in the area for source evaporation and a hike in gold re-deposition accentuate the source-to-substrate misalignment, a factor behind gate foot formation. The situation is not permanent, however, as during evaporation the metal that’s deposited on the photoresist reduces the opening and the collimating the path for the gold atoms to reach the foot. This means that as evaporation continues, the angle at which gold atoms reach the base and thus form the foot diminishes – and at a certain point, the metal thickness is tall enough to prevent the gold atoms from reaching the base directly. However, even then, some atoms can still reach the foot via re-deposition (see Figure 7).

Based on this observation, it is worth investigating whether an acceptable compromise can be reached by starting the deposition at a lower rate, before ramping up to a higher one, once a certain thickness has been deposited.

To see if that approach is worthwhile, we launched a new experiment to see whether the gate leakage can be minimised without a penalty to throughput by turning to a two-step deposition process. We began with a low deposition rate, as this should ensure a small gate foot. Then, once the gold thickness reached a point that prevents scattered gold atoms from reaching the base directly, we increased the deposition rate to shorten the process time.

Table 1. Leakage comparison between POR and the ramp-rate group.

We have compared the leakage of devices produced using the nominal rate of 0.5 Å/s with those that use this rate initially, before increasing to 1.0 Å/s for half the total gate metal thickness. The leakage for the control is -0.218 µA, a value that falls in the historic baseline of this pHEMT mask (see Table 1). In comparison, devices produced with the two-paced deposition exhibited an increase in gate leakage by around 60 percent, to an average of -0.349 µA. The two-paced growth also led to a doubling of off-current leakage. However, there is no difference in other critical FET parameters.

Although starting the deposition at a low rate before ramping this up led to a higher leakage, the leakage is still much smaller than that when producing the entire gate thickness at a high rate. It’s also quite possible that we can improve the trade-off between leakage and throughput by adjusting the ratio between the low and high deposition rates of our two-step process.

Our results are consistent with the theory that gate foot formation mostly develops early in the deposition process. It’s intuitive to reason that once the metal in the resist opening has built up to certain level, gold atoms will have a limited path for reaching the bottom of the opening. Based on this view, it follows that the impact of a high deposition rate will diminish after reaching a certain thickness in the resist opening.

In a nutshell, we can say that while the ramped rate leads to a high leakage, the value is still acceptable, and it comes with the crucial benefit of a higher throughput.

Further reading

K. Cheng, “Elimination of Metal Fencing by OptimizingEvaporator Dome Alignment”, IEEE Transactions on Semiconductor Manufacturing. 33 November 2020.