Lumerical improves design and simulation accuracy for imec silicon photonics platform

Lumerical has developed a compact model library of active and passive photonic elements calibrated to imec's iSiPP50G silicon photonics process to improve design accuracy and reliability.

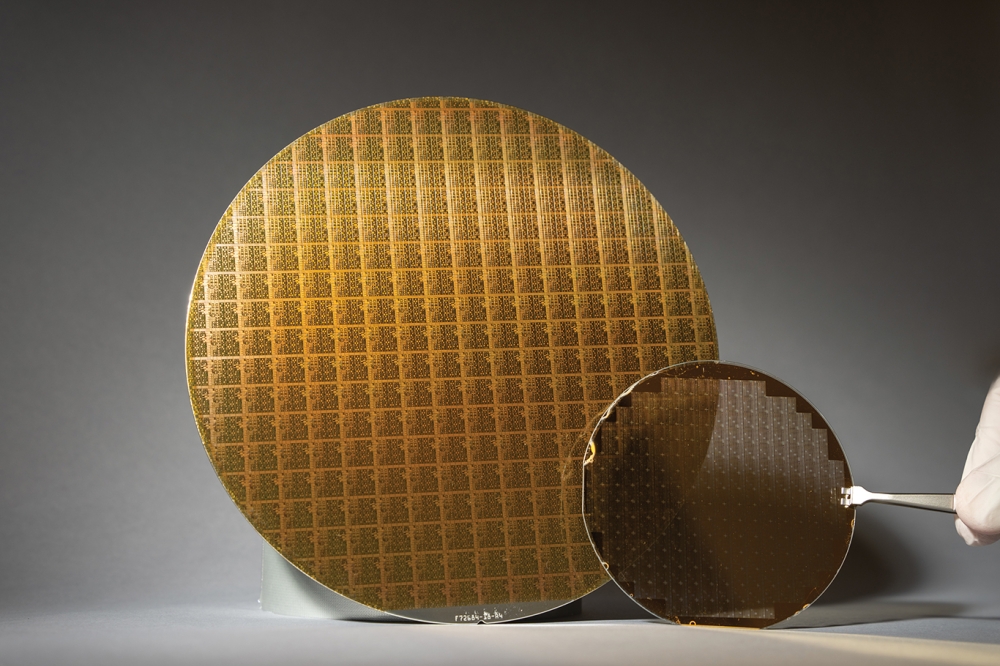

Lumerical has announced the availability of a calibrated compact model library (CML) for imec's 50Gb/s wafer-scale integrated silicon photonics platform (iSiPP50G) and process design kit (PDK). The Lumerical iSiPP50G CML enables circuit designers to accurately simulate and optimize photonic integrated circuit (PIC) behaviour and performance prior to fabrication, in order to reduce costly design errors and enable first-time-right designs within Lumerical's PIC simulator, INTERCONNECT.

"By combining measured data from multiple imec wafer runs with key operating parameters extracted from our component level simulation tools, we can generate calibrated compact models for each component that chip designers can use to design, simulate, and optimise photonic integrated circuits," stated Dr. James Pond, CTO at Lumerical. "The models are a critical aspect of PDK driven design, enabling designers to focus on circuit performance rather than component design and to align design intent with fabrication characteristics, reducing design iterations and development costs."

The iSiPP50G process offered by imec includes active modulators and photodetectors capable of operating reliably at 50Gb/s NRZ. The process is positioned to address the high performance, low power requirements of Nx100Gbs telecom and datacom transceivers, along with low cost, highly integrated sensing and LiDAR applications. The iSiPP50G PDK contains over 50 active and passive components with corresponding calibrate compact models.

"We are excited about the inclusion of the CML for INTERCONNECT in the iSiPP50G PDK. imec aims to provide a robust ecosystem for our users to develop innovative photonic devices and applications," said Philip Christie, Leader of the Business & Technology Strategy Group, imec.IC-link. "PDK-driven design methods and processes are critical for silicon photonics to meet the reliability and cost targets needed for widespread commercial adoption, and accurate chip level simulation models are a critical aspect of the PDK offering."