Bringing silicon carbide to the masses

Turning to CVD for the growth of cubic SiC on silicon slashes material costs and delivers a hike in the scale of production

BY GERARD COLSTON AND MAKSYM MYRONOV FROM ADVANCED EPI MATERIALS AND DEVICES

SiC is well-established as an ideal compound semiconductor material for applications in power electronics, harsh environment sensing and biomedical devices. It excels in these areas because of its wide bandgap and strong bonding structure, attributes that allow it to operate at higher temperatures, block higher voltages and withstand even the nastiest of chemicals.

Manufacture of SiC devices tends to employ native substrates, which have commercially available since the early 1990s. This foundation is not ideal, however, as it is pricey "“ it can be a few orders of magnitude more expensive than silicon wafers. It can also be plagued with device killing defects, and it is limited in size. Although substrates are getting larger, by the end of last year the maximum diameter of commercially available SiC was only 150 mm.

Figure 1. The crystal structure of 3C-SiC has the same basic structure as that of silicon and diamond. The red spheres represent silicon atoms and the black represent carbon. The cube shows the cubic unit cell.

An attractive way forward is to grow SiC on silicon. This slashes the cost of the substrate, which can now have a size of 300 mm or more. When grown on this platform, the SiC films have a cubic crystal structure, and are known as 3C-SiC (see Figure 1). This orientation is less common than the 4H and 6H polytypes used today to manufacture various compound semiconductor devices, such as LEDs, power diodes and transistors.

Epitaxial growth of 3C-SiC on a silicon substrate has many commercial advantages, but process engineers have failed to fulfil its promises of low costs and high volumes. Progress has been held back by the high temperature of the conventional growth process employed to grow high-quality 3C-SiC on silicon. Typical temperatures are 1390 °C, and this restricts growth to non-standard, high-maintenance hot-wall CVD reactors that lag behind the capability of those associated with traditional silicon growth technology. Growth temperatures are so high that they are very close to the melting temperature of silicon, causing several issues associated with the maintenance and lifetime of the CVD reactors.

Adding insult to injury, high growth temperatures produce significant thermal stresses between 3C-SiC and silicon. This warps the wafers, making them unsuitable for wafer-scale device fabrication (see Figure 2).

To reduce the cost per wafer, many SiC device manufacturers have moved to multi-wafer reactors to increase throughput. However, it is tricky to realise satisfactory wafer-to-wafer uniformity, yield takes a hit, and there is a need to use far larger chambers.

Figure 2. A typical cross-section of a 100 mm diameter high-temperature grown 3C-SiC epi-layer grown using a traditional high-temperature process. The thermal stresses cause bowing of the wafer.

So what's changed?

The founders of Advanced Epi started addressing these concerns at the University of Warwick, led by Maksym Myronov. Within the research group, efforts over the last eight years have been directed at the development of novel growth processes for various group IV semiconductors, including SiGe, germanium, SiC, GeSn and GeSnSi.

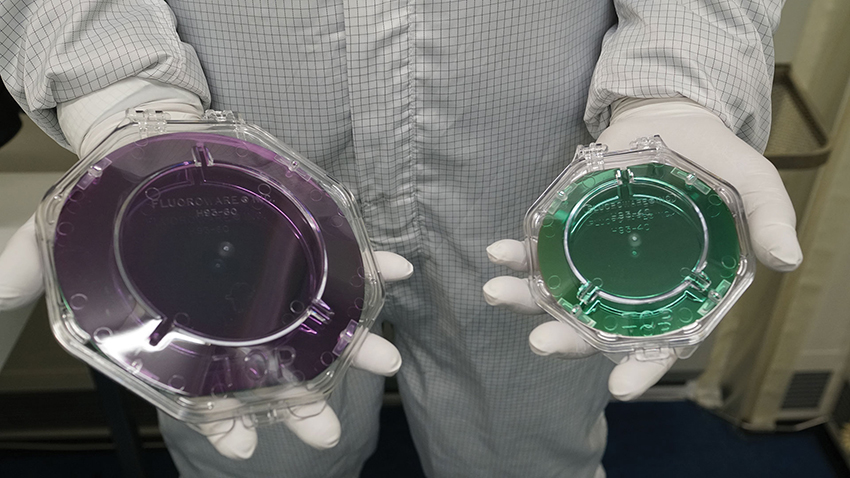

Figure 3. A 100 mm diameter 3C-SiC-on-silicon (001) epiwafer grown using Advanced Epi's low-temperature growth process. The mirror-like surface indicates low roughness. The film's colour is caused by the interference of light within the semi-transparent 3C-SiC epi-layer. It is an indicator of the excellent thickness uniformity across the wafer.

During the last few years, attention has turned to SiC, with the focus on commercial viability. Aware of the downsides of the hot-wall CVD growth process, the team has looked to the silicon industry for a solution.

Success has followed, with research unveiling high-quality crystalline growth of 3C-SiC at reduced growth temperatures.

A spin-off, Advanced Epi Materials and Devices Ltd, followed, where both authors have leading roles. Together, we have spent the last six months overseeing the development of a wafer-scale process, improving material properties and refining the reproducibility of 100 mm diameter silicon wafers (see Figure 3).

Our growth process addresses the issues of scalability and cost with a novel, low-temperature growth process that takes place on standard silicon wafers (see Figure 4). Cubic SiC is grown at 1200 °C, a temperature low enough to allow the process to be carried out in any standard silicon-based cold-wall CVD system, such as an ASM Epsilon tool.

Merits of the single-wafer reactors used in the silicon industry include high throughput, uniform growth across a large diameter wafer, and excellent wafer-to-wafer reproducibility. These virtues deliver many advantages over the traditional high-temperature growth process of 3C-SiC, such as higher volume production, superior material quality, integration with other group IV and III-V semiconductors grown on silicon or silicon-on-insulator wafers, and scalability up to 300 mm wafers and beyond. An additional advantage is that as we use standard silicon-based growth processes, we will be able to offer 3C-SiC on silicon material on a similar scale and cost to that of silicon epitaxy, once we have scaled up to volume production.

Figure 4. Advanced Epi's low-temperature process is capable of growing very thin, crystalline 3C-SiC films suitable for virtual substrates and sensitive sensing devices. Thicker layers of several microns are suitable for power electronic devices.

The high crystalline quality of our 3C-SiC epilayers has been verified by in-depth characterisation. Studies show that our monocrystalline 3C-SiC is state of the art, with a surface roughness below 2 nm, even for growth rates exceeding 10 mm per hour (see Figure 5).

Another advantage of the lower growth temperature process is a significant reduction in residual wafer bow. Accurate measurements using stylus profilometry reveal that warp is not more than 30 mm for 3C-SiC grown on standard thickness, 100 mm diameter silicon wafers with an epilayer thickness of 500-1000 nm (see Figure 6).

Epiwafers as flat as this can be used directly for wafer-scale device fabrication and other processes "“ there is no need for complex techniques to compensate for bow. This suppression of wafer bow stems from the almost complete release of strain in the 3C-SiC epilayers, and minimisation of the thermal mismatch between the epilayer and the silicon substrate. If it is warranted, further reduction in wafer bow may be accomplished with standard compensation techniques used in the silicon industry, such as selective epitaxy or growing on thicker substrates.

Strengths of our 3C SiC include an unusually high resistance, an intrinsic room-temperature sheet resistance that exceeds 200 kΩ/sq, and an opportunity to introduce electrically active impurities into 3C-SiC films during epitaxy. Thanks to the latter, it is possible to produce n- and p-type 3C-SiC without having to resort to post-growth ion implantation or high-temperature annealing. This paves the way for the fabrication of a range of more complex 3C-SiC based electronic devices.

What applications?

Our 3C-SiC material is suitable for a range of applications. Its potential scale and competitive cost make it ideal for very high volume device production, where the advantages of 3C-SiC are required, but affordability plays a big factor. Due to these strengths, one area that we are targeting is sensing in harsh environments. For devices that range from simple temperature or pressure sensors to photodiodes with a spectral responsive ranging from less than 200 nm to around 550 nm, our 3C-SiC can form the basis of a new range of products that combine operating temperatures exceeding 500 °C with the capability to handle corrosive atmospheres and environments with thermal and mechanical shocks.

Figure 5. The root-mean-square roughness of Advanced Epi's 3C-SiC-on-silicon epi-wafers can be below 2 nm, according to atomic force microscopy scans of the surface. vices.

These properties are desirable for many applications within industrial, automotive and aerospace sectors. Our material can meet the cost and volume requirements, with tests showing no structural degradation to 3C-SiC epilayers during prolonged annealing at temperatures above 1000 °C.

The chemical resistance of 3C-SiC makes it an ideal material for various microelectromechanical systems (MEMS). Production of these devices can often involve the formation of suspended structures, which tend to be fabricated with a range of complex processes.

As 3C-SiC resists the effects of almost all chemical etchants, it is straightforward to fabricate suspended micro-wires for temperature sensing, and to make membranes for pressure transducers (see Figure 7 for an example).Another potential market for 3C-SiC on silicon is as a template for GaN growth. Like SiC, GaN exhibits polytypism, with commercial blue and ultra-violet LED production involving growth of the hexagonal phase (see table 1 for material properties). When 3C-SiC is grown on a silicon (111) substrate, this produces the ideal template for hexagonal GaN, due to a lattice mismatch of approximately 3.5 percent at the SiC-silicon interface. Reducing mismatch between GaN and silicon is valued highly, because it holds the key to reducing the intrinsic defects found in GaN when this material is grown on highly mismatch substrates, such as silicon or sapphire. Note that the lattice mismatch between GaN and silicon is about 17 percent at room temperature.

Figure 6. Wafer bow across a 500 nm-thick, 3C-SiC-on-silicon epiwafer grown on a standard 525 µm thick, 100 mm diameter silicon wafer. Parabolic wafer bow of 20 µm is measured up to the edge of the wafer.

One attract alternative is to use our material as a template for the growth of cubic GaN. This polytype has been very difficult to grow and nigh-on impossible to commercialise, but it can offer some exciting advantages for pushing emission of nitride LEDs to longer wavelengths and addressing the "˜green gap' "“ the unwanted decline in LED efficiency from blue to green, where the human eye is at its most sensitive. The challenge is that before cubic GaN can address the green gap, growers of this material will need to overcome many challenges before it is suitable for producing product. The use of our technology is not limited to a range of optoelectronic devices. GaN grown with our technology can also aid high frequency and power devices, thanks to its increased thermal conductivity that increases the capability of the device to dissipate heat.

What's next?

Our technology promises to break new ground by driving the integration of SiC into the mass semiconductor market. As our 3C-SiC-on-silicon heterostructure can be implemented in several device structures with standard silicon processing techniques, it has the potential to find application across a wide range of sectors (see Figure 9). Although we are in our infancy, we are developing the technology at an incredible rate, thanks primarily to the scale of the silicon-based growth method. Efforts are now being directed at developing various sensing device structures in-house, utilising the properties of 3C-SiC to fabricate temperature, pressure and ultra-violet sensors for applications in demanding environments.

To bring this material to the required commercial specification, using only standard silicon-based foundry processes, we are working with UK and international device manufacturers.

We are also working closely with growers of GaN to demonstrate that 3C-SiC material is a great foundation for the growth of both hexagonal and cubic GaN. These efforts demonstrate that our technology delivers the predicted advantages over other substrates, in terms of final device characteristics.

Figure 7. Suspended 3C-SiC microwires (left) and a square membrane (right) for MEMS applications fabricated using the anisotropic wet etching of the underlying silicon. As the 3C-SiC is resistant to almost all chemical etchants, fabrication of suspended structures is significantly easier than with other materials.

While developing our processes, we are constantly looking for new opportunities and collaborators in any field that could benefit from our 3C-SiC epiwafers. Our 100 mm epiwafers are ready for preliminary trials, and we can grow material to a range of specifications for different applications, including: thickness, crystal orientation and electrical properties.

Due to demand from our customers and collaborators, we are currently scaling up our production to include 150 mm diameter wafers, and under special request we can go up to 200 mm with the facilities that we currently have available to us.

Figure 8. 3C-SiC is suitable as a virtual substrate for both cubic and hexagonal GaN, depending on the crystal orientation of the silicon substrate. In each case, lattice mismatch is approximately 3.5 percent.

Figure 9. Advanced Epi's vision is for 3C-SiC-on-silicon material to make disruptive improvements within various industrial sectors.

Table 1 Basic properties of relevant semiconductor structures. Both the cubic and hexagonal form of GaN are shown. Although 3C-SiC has a lattice parameter of 4.36 à…, when it is grown on the (111) orientation its surface lattice constant is the same as that of 4H-SiC (3.073 à…).