Imec breaks down 3D memory barriers

Integrating a high mobility InGaAs channel to 3D NAND Flash memory is set to solve the read speed issues plaguing Samsung, Toshiba and more.

Stacking memory cells beyond 100 layers could lead to a terabit memory chip, but limited channel mobility is a key stumbling block.

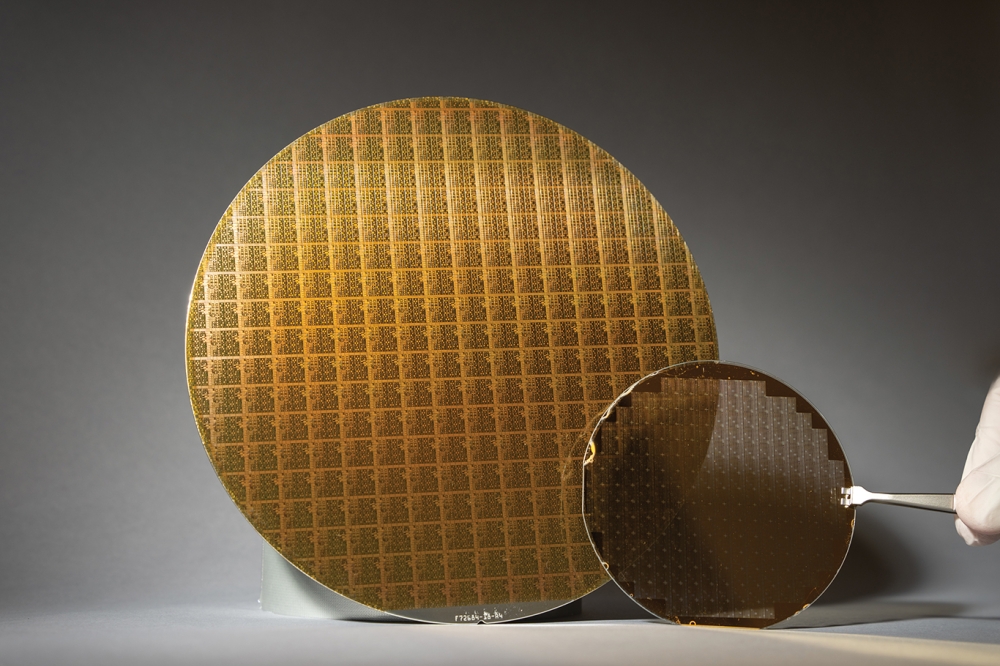

In a world first, Belgium-based nanoelectronics research institute, Imec, has integrated a high mobility InGaAs channel to a 3D vertical NAND memory structure, in a bid to banish the drive current issues surrounding today's 3D NAND Flash devices that use a poly-silicon channel.

Right now, key NAND Flash manufacturers are replacing conventional planar NAND with 3D NAND to overcome problems such as cell to cell interferences and read noise associated with aggressive scaling.

The basic premise of these 3D memory devices is to stack storage cells vertically to dramatically boost the bit density relative to planar NAND flash.

Alternating layers of conductive polysilicon and silicon dioxide dielectric are deposited as a vertical stack, with channels then etched through the layers.

Hollow poly-silicon tubes, known as 'macaroni channels', are then deposited within the etched channel.

Since Samsung delivered the first mass-produced, 24-layer memory device in 2013, progress has been rapid.

The South Korean conglomerate unveiled its latest 'vertical' NAND 48-layer chip in August last year while Toshiba and SanDisk also recently introduced a 48-layer flash memory device.

At the same time, Intel and Micron have released a 32-layer chip, and ultimately, industry players intend to create 100-layer stacks to achieve 1 Tbit memory devices

But like the planar predecessors, these 3D NAND device's days are also numbered, and it's all down to the poly-silicon macaroni channel.

As Arnaud Furnemont, memory department director at Imec, points out, the drive current of these 3D devices - with poly-silicon macaroni channels - decreases linearly with the number of memory layers.

"The resistance in poly-silicon is more or less proportional to the length of this channel, so if [industry players] keep stacking up the layers, at some point device read speed will just become too slow," he says.

As Furnemont concedes, it is difficult to predict at what point this will happen but as he says: "Companies have announced 48 layers, and 64 layer devices are in sight on the roadmap."

"I think this number of layers will be fine but above 64 layers and by 100 layers, it will be interesting to have an alternative channel," he adds.

Given this, Imec has been looking to swap the poly-silicon channel with a III-V alternative with a higher electron mobility. SiGe, with its high hole mobility, didn't fit the bill, so the researchers turned to InGaAs.

"InGaAs provided the right trade-off between electron mobility and bandgap," says Furnemont. "And by changing the ratio of indium and gallium we can play on this trade-off."

In this latest work, the researchers have fabricated a three-layer memory stack into which 45 nm channel openings are etched and an InGaAs channel then formed, using MOCVD.

According to Furnemont, the resulting devices out-performed the poly-silicon equivalent by an order of magnitude, and critically, memory characteristics, including programming, erase and retention were maintained.

![]() Typical ID-VG: In0.6Ga0.4As presents improved ID-VG characteristic. Ion/Ioff ratio of 3 order of magnitude is sufficient for typical NAND operation.

Typical ID-VG: In0.6Ga0.4As presents improved ID-VG characteristic. Ion/Ioff ratio of 3 order of magnitude is sufficient for typical NAND operation.

But clearly a three-stack device is a far cry from industry's latest 48-layer versions. And what's more, the InGaAs channel was actually solid, rather than the required macaroni conformity.

As Furnemont puts it: "Our InGaAs channel fills the entire hole so to make the device relevant we need to convert the process from a full channel to macaroni channel."

Given this, he and fellow researchers now hope to develop an atomic layer deposition process so they can create a five-layer structure with the required macaroni channel.

"Apart from a few exceptions, ALD hasn't really been developed for III-V materials, and there isn't a full solution here yet," he says. "But we are working with a supplier to develop III-V ALD. So far we have structural data but no electrical data yet."

Furnemont also expects researchers to experiment with epitaxial growth, ALD and annealing to achieve progressive crystallisation of InGaAs macaroni channels in 3D NAND structures.

Beyond channel resistance issues, the researchers may also look at the problem of stresses in the memory stack. Defects form at the interface of the channel and silicon dioxide layers but adding a thin high k layer here could resolve this problem.

Given a full solution to 3D NAND's integration issues has yet to come, is Furnemont still hopeful that the likes of Samsung and Toshiba will adopt Imec's processes? Indeed, these and other memory developers have massive research and development teams working on the very same problems.

"We still believe that channel mobility is not the worst part of these next generation [3D NAND] devices, and maybe a cheaper [memory] solution will be discovered and implemented at some point in time," says Furnemont.

"But if we can deliver a full integral solution for this approach then [industry players] will definitely look into this more deeply, and who knows, may apply it to their products," he adds.