The promise of truly two-dimensional transistors

BY AMIRHASAN NOURBAKHSH, LILI YU, AHMAD ZUBAIR AND TOMàS PALACIOS FROM MASSACHUSETTS INSTITUTE OF TECHNOLOGY

The days of the silicon transistor are numbered. Increasing the transistor count on an IC through a reduction in the size of the device, and the power required to operate it, may continue throughout this decade. But if the march of Moore's law is to continue in the 2020s, it will require the introduction of alternative materials with superior characteristics to silicon, allied to the development of new device architectures.

Much of the effort associated with the development of devices sporting new materials has focused on high electron mobility III-Vs, such as InGaAs, that can be paired with germanium, a material that can transport holes at high speeds. Transporting carriers at higher mobilities than silicon is a tremendous asset, as it can enable a cut in the transistor's operating voltage while maintaining the current flowing through this device. Lowering the voltage is highly beneficial on two fronts: it reduces chip heating; and it cuts the power consumption per transistor, enabling mobile technologies to introduce more powerful ICs while maintaining battery life.

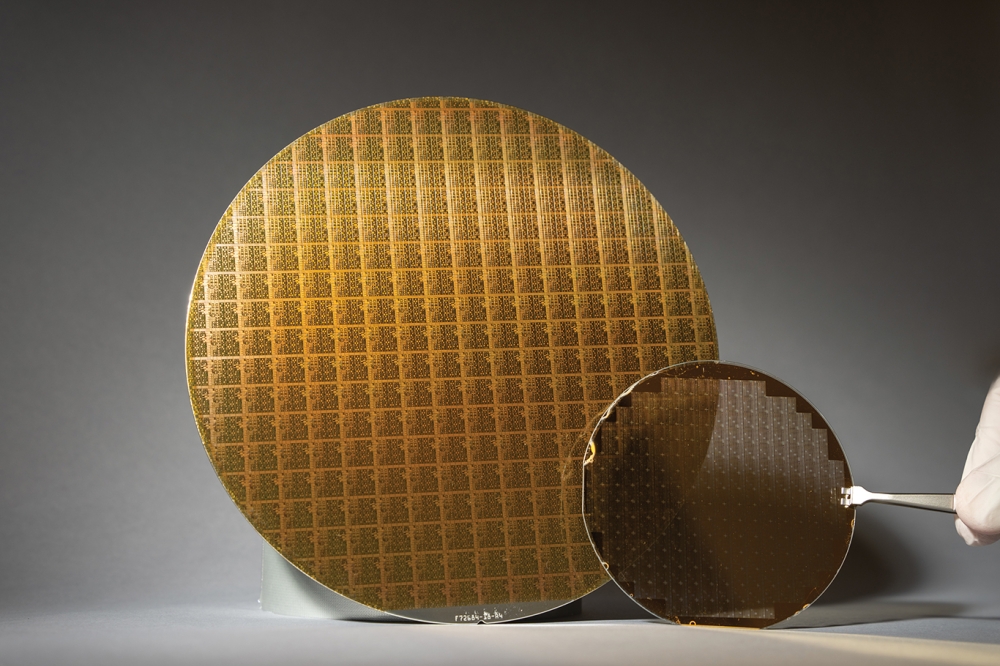

Device fabrication typically involves the deposition of films of either germanium or III-V heterostructures onto silicon substrates, which may have modified surfaces. The high mobility materials may be thought of as two-dimensional, given that the layer can be just a few nanometres in thickness and extend over areas of many microns. However, the reality is that these materials are quasi-low-dimensional semiconductors that are riddled with numerous dangling bonds (see Figure 1).

It is possible to produce transistors with truly two-dimensional materials by turning to a different class of semiconductors. Options for atomically thin films of semiconductors include transition metal dichalcogenides such as MoS2. Merits of these materials are not limited to an absence of dangling bonds, and include a high degree of mechanical stability.

At the Massachusetts Institute of Technology (MIT), our team is developing technologies based on MoS2 that will enable a shrinking of the size of these transistors, so that their channel length is less than 10 nm. Another aim of ours is to demonstrate the use of these two-dimensional transistors in circuits and systems for large-scale flexible electronics applications.

We have selected monolayer and few-layer MoS2 for device development. This material has a large band gap of 1.85 eV that equips the FET with an extremely low off-current. What's more, when this class of transistor is built from a monolayer or a few layers of MoS2, it is effectively an ultra-thin body FET, and thus immune to short channel effects. On top of this, thanks to its atomically thin body, this two-dimensional semiconductor is promising for applications requiring the integration of electronic and optoelectronic circuits on flexible substrates, such as polyethylene terephthalate (PET).

![]()

Figure 1. The crystal structure of layered MoS2 is significantly different from that of bulk semiconductors, such as silicon and the III-Vs. Unlike these more traditional semiconductors, dangling bonds do not occur in the layered crystals because of van der Waals interlayer interactions.

Another strength of the MoS2 device − and wide-bandgap, two-dimensional semiconductors in general "“ is the opportunity to combine high-performance with an ultra-low power consumption, which is attractive for Internet-of-things technologies. Incredibly low levels of power consumption are possible by optimising the transistor for sub-threshold operation. When running in this regime, the on-current near the threshold voltage is governed by the sub-threshold swing, rather than carrier mobility. A very low off-current results from the use of wide bandgap, two-dimensional materials.

Recently, we have demonstrated a double-gate MoS2 FET with a 15 nm channel length. The MoS2 layer is formed by CVD, via sulpharization of MoO3, using perylene-3,4,9,10-tetracarboxylic acid tetrapotassium salt (PTAS) as seed.

A role for grapheneWith this particular architecture, the electrodes for the source and drain are in immediate contact with the channel, and must be as thin as it to avoid disrupting the electric field lines. To fulfil this requirement, we construct these electrodes from monolayer graphene. This allotrope of carbon is ideal − it forms the thinnest conductive membrane in nature, and it can sustain very high current densities of around 109 A cm-2.

The most important step in the fabrication of our double-gate MoS2 FET is the high-resolution patterning of graphene, which defines the transistor's source-drain length (see Figure 2 (a) for a diagram of the structure). To perform this step, we stack a graphene monolayer on the MoS2 film, before patterning it by electron-beam lithography, using a poly(methyl methacrylate) resist. High-resolution patterning results from developing this PMMA at a low temperature. By employing a cold development process, we are able to open well-controlled trenches with widths as low as 10 nm.

Selective etching of the graphene monolayer follows. This step is critical, because it must avoid imparting any damage to the underlying monolayer or few-layer MoS2 surface. We have fulfilled this requirement by developing a mild etching process that uses oxygen plasma pulses, rather than a continuous plasma exposure. Facing the samples away from the plasma flux avoids direct exposure to the energetic plasma particles.

Adopting this approach allows us to precisely etch the graphene layer while making minimal impact on the MoS2 channel (see Figure 2 (b) for an AFM image of the resulting surface). The method is actually well suited to forming contacts on any ultra-thin body transistor; it is comparable to the metal dry-etching process used to fabricate source, drain and gate electrodes in a conventional device technology, and it is CMOS compatible.

Employing graphene for the channel has an additional benefit, as it allows doping to vary the work function of this material over a wide range. This means that the process can potentially be used for both n- and p-FET technology.

Comparing the transfer characteristics of our 15 nm, 30 nm and 60 nm single-gate MoS2 FETs reveals that devices with the two shorter channel lengths suffer from short-channel effects, which lead to a hike in the off-current and large values for sub-threshold swing (see Figure 2(c)). This can be lowered, however, by adding a top gate structure to form a double-gate configuration. Measurements show that a 15 nm MoS2 FET with a double-gate configuration has an on-off current ratio of about 106, an on-current of typically 50 µA/ µm, and a minimum sub-threshold slope of 90 mV/dec at a drain-source voltage of 0.5 V.

![]()

Figure 2. (a) The cross-section of short-channel, graphene-contacted MoS2"“FET. (b) Atomic force microscopy images showing 10 nm, 15 nm and 20 nm graphene slits. (c) Transfer characteristics of 15 nm, 30 nm and 60 nm single-gate MoS2-FETs with graphene source and drain contacts. (d) The double-gate MoS2-FET produces record performance values, including a sub-threshold swing of 90 mV/dec and an off-current of about 10 pA/µm.

Selective etching of the graphene monolayer follows. This step is critical, because it must avoid imparting any damage to the underlying monolayer or few-layer MoS2 surface. We have fulfilled this requirement by developing a mild etching process that uses oxygen plasma pulses, rather than a continuous plasma exposure. Facing the samples away from the plasma flux avoids direct exposure to the energetic plasma particles.

Adopting this approach allows us to precisely etch the graphene layer while making minimal impact on the MoS2 channel (see Figure 2 (b) for an AFM image of the resulting surface). The method is actually well suited to forming contacts on any ultra-thin body transistor; it is comparable to the metal dry-etching process used to fabricate source, drain and gate electrodes in a conventional device technology, and it is CMOS compatible.

Employing graphene for the channel has an additional benefit, as it allows doping to vary the work function of this material over a wide range. This means that the process can potentially be used for both n- and p-FET technology.

Comparing the transfer characteristics of our 15 nm, 30 nm and 60 nm single-gate MoS2 FETs reveals that devices with the two shorter channel lengths suffer from short-channel effects, which lead to a hike in the off-current and large values for sub-threshold swing (see Figure 2(c)). This can be lowered, however, by adding a top gate structure to form a double-gate configuration. Measurements show that a 15 nm MoS2 FET with a double-gate configuration has an on-off current ratio of about 106, an on-current of typically 50 µA/ µm, and a minimum sub-threshold slope of 90 mV/dec at a drain-source voltage of 0.5 V.

Benchmarking the performance of MoS2 channel FETs, and considering long-channel and short-channel regimes, indicates that our transistor has the shortest operating channel length. Another of our transistor's attributes is that it produces a record minimum sub-threshold swing (see Figure 3 (a)).

![]()

Figure 3. The MoS2 channel transistors produced at MIT set a new performance benchmark, according to values for sub-threshold swing and drain-induced barrier lowering.

Our MoS2 FET also has excellent immunity to short-channel effects, even when it is formed with a single gate. This strength is highlighted by the benchmarking of the drain-induced barrier lowering (DIBL), which is an indication of change in threshold voltage with respect to drain-to-source voltage. In a long channel FET, the energy barrier, as well as threshold voltage between the drain and channel, remains constant irrespective of drain bias − this is not true for the short channel case. Adding a second gate increases robustness against short-channel effects, and results in a device that performs, in many aspects, as well as much larger state-of-the-art silicon-on-insulator transistors, despite the lack of systematic optimization. Thanks to the high on/off ratio and excellent sub-threshold characteristics, further device scaling should be possible.

The Achilles' heel of the MoS2 transistor is its high contact resistance, which stems from the Schottky barriers used for electron injection. To mitigate this, low-work-function metals are often used for the source and drain ohmic contacts on n-type MoS2. This helps to lower the Schottky barrier significantly, but the contact resistance remains relatively large "“ it is in the kΩ.m range "“ and this limits device performance.

The solution is to heavily and locally dope MoS2 in the contact region, because this reduces the energy barrier and eases carrier injection into the channel. Doping allows a tuning of the work function of graphene from 4 eV to 5 eV, a range wide enough to cover the work functions of several metals that are commonly used in CMOS technologies.

Increasing complexityOur recent development in the modelling and design automation of MoS2-based devices and circuits has allowed us to move up to another level of circuit complexity. We can make various device components and circuits (see Figure 4), including a single-stage inverter, and multi-stage combinational and sequential logic circuits (NAND, NOR, AND, OR, XOR, XNOR, and latch).

![]()

Figure 4. (a) One opportunity for the MoS2 thin film transistor is as part of a backplane circuit for an organic LED display (left). (b) Optical image of a logic circuit chip. (c) Transient performance of a latch with a memory effect. The latch, which was designed as part of this work, uses two cross-coupled inverters and pass transistors. When the clock signal is low, the latch output follows the input, but when the clock is high, the feedback loop is enabled and the latch operates in the hold mode.

One of the many system-level applications being pursued for large-scale MoS2 electronics is the backplane circuit for flexible organic electronics. Our group is working in this area, developing a technology involving the use of large-area synthetic MoS2 as the active semiconductor to fabricate a thin-film transistor (TFT) backplane for flexible, transparent, organic LED displays.

These backplane circuits use two TFTs and a storage capacitor to control each pixel and trigger the luminescence (see Figure 4 (a)). One TFT starts and stops the charging of the storage capacitor, while the second acts as a voltage source in the saturation region, delivering a constant current to the pixel. Organic materials with multi-layered heterostructures are deposited for OLED integration, before a transparent electrode is added on top of the organic materials. Another system-level application that we are currently working on is a self-powered RF sensor node, which includes an energy harvester, rectifier network, a sensor node and logic units (see Figure 5(a)). A key component in the energy power management and energy harvesting circuits is the diode, which is used for RF energy harvesting and rectification.

For this work we use a gated diode. This device, which is formed by connecting the gate and the drain of an E-mode MoS2FET, exhibits an excellent rectifying, and can operate over a wide range of frequencies, spanning 1 Hz to 13.6 MHz. The low-frequency response can be very helpful when interfacing the system with a piezoelectric energy harvester device, where 13.56 MHz is the base carrier frequency used in short-range communications for near-field, communication-type, radio-frequency identification (RFID) applications.

In this particular application, a near-field communication-type reader supplies AC power, via inductive coupling, to the inductor-capacitor tank circuit integrated in the RF sensor chip. The rectified and regulated voltages serve as supply voltages for the sensor nodes. Environment information acquired by the sensor is processed by the digital circuit and then stored as data in the memory. This data is transmitted via changes in the output frequency of the demodulator.

High performance levels are possible with our test chip, which contains some of the most important components, including half-wave rectifiers and switched-capacitor DC-DC converters (see Figure 5(b)). We have also designed and fabricated a wireless link and driver circuit on a flexible substrate (Figure 5(c)), and used an LED load to demonstrate milliwatt-scale inductive power transmission and MoS2 rectifiers.

![]()

Figure 5. (a) Design of a self-powered RF sensor system. (b) Optical image of an RF-powered LED node. (c) Integration of the RF LED node with a flexible coil.

Having combined all these functions on a single chip, our next goal is to move to a flexible substrate "“ and on this eventually form ultra-short-channel transistors that will enable a high-performance, multifunctional platform for emerging technologies. This will not be easy, however. To succeed, we first need to develop CMOS-compatible doping methods for efficient, high precision local doping and contact engineering of MoS2 transistors, so that we can take the performance of this class of electronics to a new level. This will be the first step on a long road to the acceptance and implementation of MoS2 transistors by the mainstream electronics industry, which must draw on new materials to continue to ensure progress.