PICs: Options for lighting up the chip

To produce the best PIC, is it better to take an InP laser and unite it with a silicon photonic chip, or make many components in InP, before uniting with silicon?

As all those that work with photonic integrated circuits (PICs) know, the latter is not actually true: a silicon laser is still a distant dream, because this material is an incredibly inefficient light emitter. So, to create a photonic chip today, the laser is made from compound semiconductor materials. In fact, it is possible to build the entire photonic chip from this material system. It is an approach that can deliver great commercial success, as shown by Infinera. However, it is not the only option, with one common alternative being the integration of the III-V laser with a silicon chip.

At the inaugural PIC International Conference, two differing views were offered on the pros and cons of different approaches for equipping a photonic chip with a light source.

Speaking at the session entitled Where should the laser go?, Shinji Matsuo from NTT Photonics Laboratories outlined a cost-effective approach for incorporating InP-based buried heterostructure lasers on silicon substrates; while Fang Wu from ArtIC Photonics championed the production of an InP circuit that is subsequently united with silicon.

Matsuo, a Senior Distinguished Researcher at the NTT Device Technology Laboratories, gave a talk describing the development of a pair of devices: a distributed feedback (DFB) laser on SiO2-on-silicon for datacom applications, and a novel photonic laser for use in computer communication. In both cases, the laser had a high modulation efficiency that resulted from the high degree of optical confinement.

The spokesman for NTT began his presentation by highlighting two findings from a Cisco study of datacentre traffic. This piece of market research determined that more than three-quarters of data-centre traffic is directed internally, and global data centre traffic is increasing at a double-digit rate.

For the data-centre application, today's workhorse is the VCSEL. It is used in links of about 1 m to 100 m or more, because it combines low cost with a very low power consumption. However, it may not be suitable in future, because it could struggle to cope with increases in traffic.

Matsuo believes that the increase in data traffic will be accommodated by the introduction of wavelength-division multiplexing technology in these short links. "The VCSEL is challenging, because it is difficult to control the single-mode lasing and the wavelength," argues Matsuo. He points out that the DFB laser might be better suited to this application, because it is easy to control the lasing wavelength of this source, which is well-established, given its use in telecom networks.

One of the weaknesses of the traditional DFB laser is its power consumption "“ it is much higher than that of a VCSEL. But this flaw has been overcome by NTT's lasers, thanks to the use of a membrane architecture. Another attractive attribute of these lasers is their low cost, which results from production with silicon fabrication technologies.

![]()

The low power consumption of the lasers stems from an architecture that ensures a high degree of optical confinement. Many developers of InP-on-silicon lasers "“ including teams at the University of California, Santa Barbara, Ghent, and Leti "“ employ a vertical pin junction and a III-V layer typically 3 µm-thick. This leads to an optical confinement factor ranging from 3-9 percent. In comparison, the NTT laser has an optical confinement factor of around 50 percent, thanks to a lateral pinjunction that incorporates a III-V layer that is just 250 nm-thick.

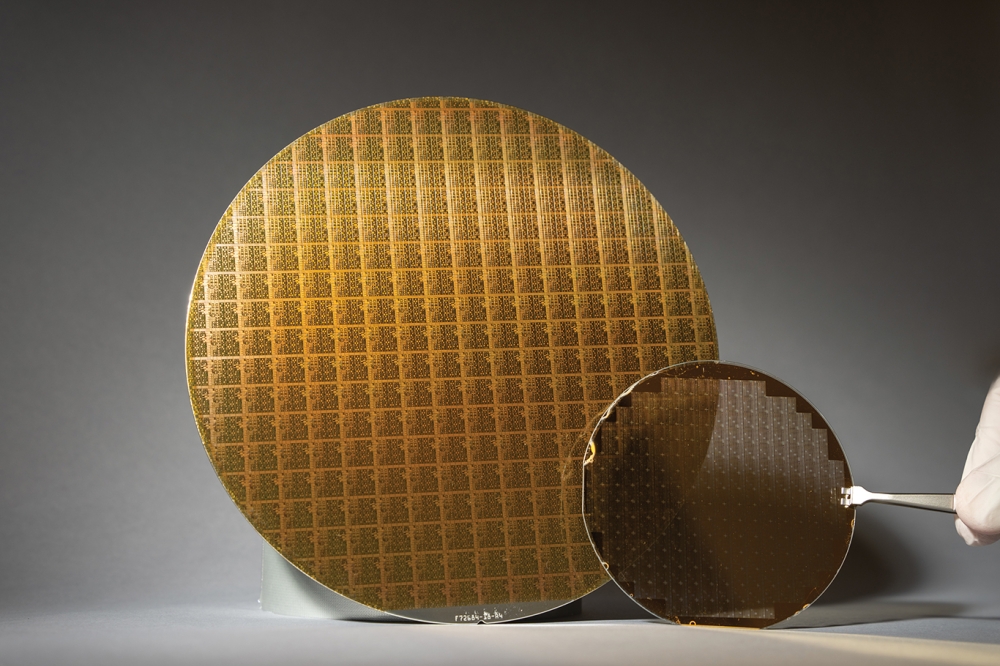

Wafer bonding unites the lasers with the silicon substrates. As large SiO2-on-silicon substrates are used, several InP wafers are bonded to them. If the bonding is carried out after the fabrication of the buried heterostructure, fine alignment is required in the bonding process. So, to avoid this issue, wafers are bonded before forming the buried heterostructure (see Figure 1).

To create the lateral injection lasers, after the buried heterostructure has been defined, silicon ion implantation defines then-type region and the p-type region is formed via zinc diffusion (see Figure 2). "We slightly etch the InP layer to increase the coupling efficient to the grating," explains Matsuo.

The lasers that result operate at up to 100 °C, have a maximum output power of 0.93 mW at 25 °C, and produce a peak wall-plug efficiency of 9.7 percent. Driven at 25 °C with a 25.8 Gbit/s non-return-to-zero signal, their key figure-of-merit is 171 fJ/bit.

Recently, NTT's engineers have improved upon this by combining their DFB laser with a distributed Bragg reflector and a spot-size convertor. It is based on a 300 µm laser taper, which reduces in width from 1.5 µm to 0.1 µm. Although the taper introduces a loss "“ it is calculated to be 1.7 dB "“ the device delivers 131 fJ/bit when driven with a 25.8 Gbit/s non-return-to-zero signal.

Matsuo claimed that a far lower figure of 7 fJ/bit is required for "computercom" applications. "So we employ photonic crystal cavities."

Photonic crystal lasers may be made by forming holes in a slab of InGaAsP. But this quaternary has its downsides, including a low thermal conductivity and a lack of carrier confinement. These weaknesses make it challenging to realise room-temperature, CW operation. Although increasing the Q-factor and reducing the active volume helps, lasers still suffer from a low output power and a low modulation speed.

![]()

Figure 2. Using a lateral geometry enables the team from NTT to have a high degree of optical confinement for their lasers. This leads to an increase in efficiency.

To address this, Matsuo and co-workers have developed an InP-based device that they describe as a LEAP laser "“ that is short for a λ-scale, embedded-active-region photonic crystal laser. Selecting InP, rather than InGaAsP, produces several benefits: it provides a hike in thermal conductivity from 4.2 W m-1 K-1 to 69 W m-1 K-1; it enables effective carrier confinement; and it simplifies integration with input and output waveguides.

The team's electrically driven LEAP laser on an InP substrate operated with an energy cost of just 4.4 fJ/bit when hooked-up to a 10 Gbit/s non-return-to-zero signal. Replicating these results on a silicon substrate has been challenging, with the Q-factor increasing, leading to a hike in threshold current from 4.8 µA to 57 µA. "Now we are modifying cavity design," revealed Matsuo.

Wu, Co-founder and Chief Technology Officer of the Canadian start-up ArtIC Photonics, has also considered various material systems. In her talk, she compared the strengths and weaknesses of InP and silicon: "It's not clear cut, which is why there is a debate."

According to her, the merits of InP include its strong optical and optoelectronic functionality, which must be weighed against relatively high power consumption for electronic devices made with this III-V. She argues that InP can be used in foundries, but there are compromises: "It either has too complicated a foundry process, or it can be designed to a high-volume foundry, but design flexibility is restricted."

Silicon, meanwhile, is let down by its optoelectronic capabilities, but can form superior passive circuits, and is compatible with CMOS fabrication. "So clearly we need to have both material systems combined to meet the challenge," reasoned Wu.

One option is to bring the InP laser onto the silicon substrate to create a hybrid photonics chip with an optical interface. While this addresses concerns related to emitting and receiving light, it creates issues at the edge of the network that are related to the pluggable interface. "That's a big problem," says Wu. "It does not address the foundry compatibility."

A more traditional approach, which is pursued by ArtIC, is to begin by forming all the monolithic optoelectronic functions in InP. In the case of the Ottawa start-up, the InP wafer is then flipped over and attached to another made from silicon (see Figure 3).

The starting point for this is the growth and processing of the InP epiwafer. It features "base epitaxy", a collection of layers near the substrate that are used to form coupling waveguides and passive waveguides. Active devices are grown on top, using either selective-area growth or growth-etch-regrowth. Connecting devices by waveguides avoids the need for careful alignment, and ensures design flexibility.

![]()

Figure 3. Forming lasers on silicon substrates (left) is not a foundry-compatible process. If the devices are defined on the InP substrates first (left), which is the approach that is pursued by the Ottawa start-up ArtIC, chip production can be outsourced to a foundry.

Wu says that by adopting this approach, ArtIC can realise a continuous, uninterrupted process flow from beginning to end. By using standard semiconductor etch and protection steps, and a metallisation process, PICs can be produced with short process times under a smooth production flow.

One of the major benefits of taking this particular approach is that it allows PICs to be produced in electronic foundries that churn out RFIC chips. "It helps reduce development costs, and more importantly, it is a manufacturing-ready process," enthused Wu.

She went on to outline some of the "true" building blocks that can be connected in different ways. They include a single-mode laser with a surface-etched grating that can operate at up to 10 Gbit/s; an electro-optic modulator that can deliver switching at up to 40 GHz; and a spot-size converter with a loss of less than 10 percent over the 1.49 µm - 1.63 µm spectral range.

Engineers at ArtIC have also designed Echelle gratings for wavelength division multiplexing. They can provide a channel spacing ranging from 100 GHz to 20 nm. "The noise floor is below -35 dB," explained Wu, who also detailed a coherent receiver, featuring 14 integrated components.

Like NTT, the Canadian outfit is targeting the short reach data com markets with its PIC technology. However, it believes that low-cost, high-volume manufacture will allow its technology to also serve the medium-reach access market, which requires links of 10-20 km, and the longer reach metro market that involves data transfer over distances of around 40 km.

It will be interesting to see how PICs made with ArtIC's technology, and those made using NTT's, impact the market in the coming years. Discussions of the successes that they have, and that of their rivals, is sure to be one of the talking points of PIC International in 2017 and beyond.