News Article

IQE and Penn State University to present paper on As/Sb HFETs

The presentation will describe the potential for arsenide/antimonide based materials for integration into future ultra low voltage electronic devices.

IQE plc and Pennsylvania State University will next week present a joint paper on recent key developments in compound semiconductor device technologies for low voltage transistor applications at the International Electron Devices Meeting (IEDM) in Washington, DC.

The paper, "Demonstration of MOSFET-Like On-Current Performance in Arsenide/Antimonide Tunnel FETs with Staggered Heterojunctions for 300mV Logic Applications," will be presented by Dheeraj Mohata at Penn State University.

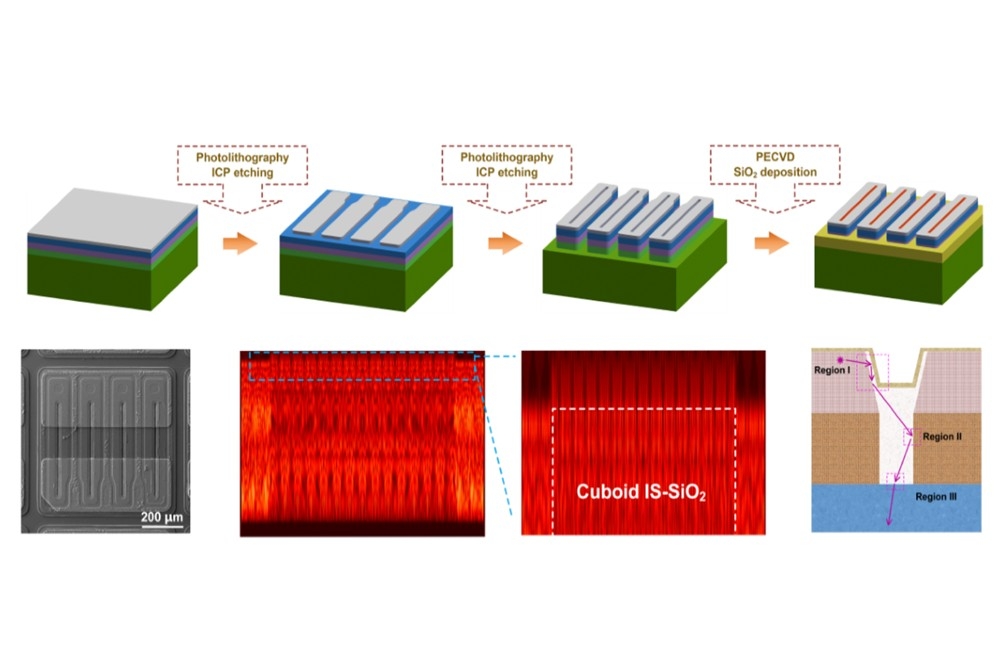

The results have experimentally demonstrated a vertical hetero tunnel Field Effect Transistor (HTFET) with a record high drive current (ION) of 190μA/μm and 100μA/μm at VDS=0.75V and 0.3V, respectively.

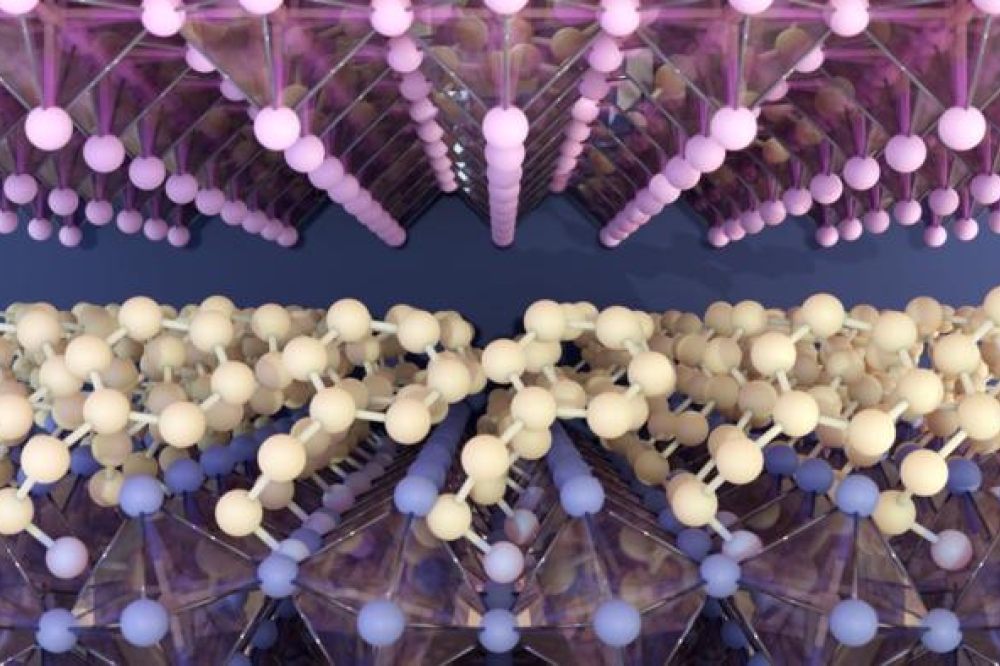

The research measured, simulated and benchmarked the performance of compound semiconductor based Tunnel-FET (TFET) with 40nm strained Si MOSFET performance for low voltage (0.3V) logic applications, demonstrating the potential for arsenide/antimonide (As/Sb) based materials for integration into future ultra low voltage electronic devices where high performance and low power consumption is a critical factor.

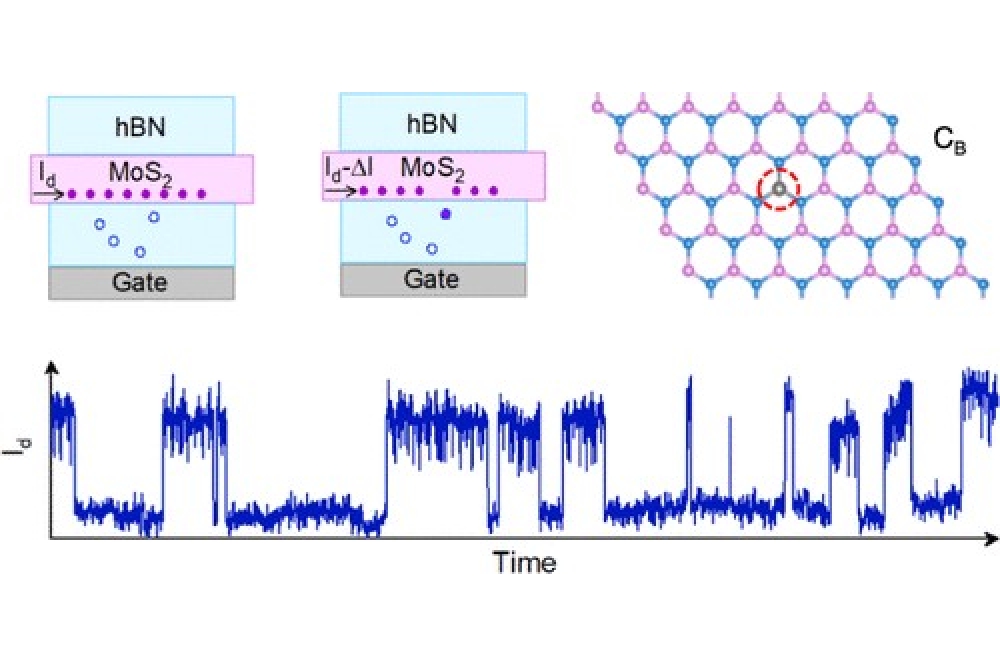

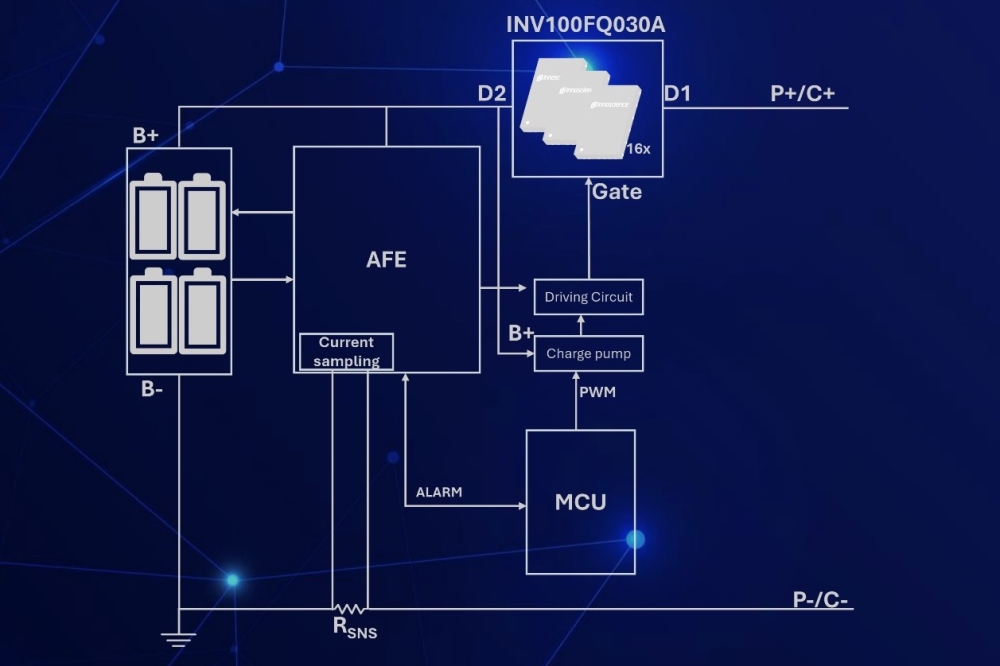

Tunnel FET is an emerging transistor concept being explored by many groups around the world. In traditional MOSFETs, the building block of digital technology, the transistor channel is turned on by injecting carriers over a gate controlled p-n junction.

This results in a gradual turn-on of the transistor and works well as long as we do not reduce the supply voltage of operation too much. In Tunnel FETs, the transistor channel is turned on by injecting carriers through a gate controlled tunnel junction. This results in abrupt turn-on of the transistors which allows us to reduce the supply voltage of operation and hence achieve significant power saving.

The biggest hurdle facing the adoption of Tunnel FETs by the mainstream semiconductor industry is that the drive current of the Tunnel FET demonstrated to date is quite low due to limitation of the band to band tunnelling rate in known semiconductors. By carefully selecting the proper combination of two different semiconductors and adjusting their composition such that their band alignment results in a staggered configuration, one can significantly increase the tunnelling rate and enhance the drive current, or ION, of the Tunnel FET. This has been achieved in a vertical HFET discussed in the presented paper and offers the potential to enable a new generation of electronics that can operate in highly energy constrained environments.

Established in 1955, the IEDM is one of the world's premier forums for reporting breakthroughs in technology, design, manufacturing, physics and the modelling of semiconductors and other electronic devices. Proceedings of the conference are published by the IEEE.