GaN HEMTs: The substrate conundrum

With GaN HEMTs, is the additional cost of a native substrate a price worth paying?

BY MOHAMMED ALOMARI FROM THE INSTITUTE FOR MICROELECTRONICS STUTTGART (IMS CHIPS)

Silicon, the incumbent technology for power electronics, has its limitations. They includes its failure to provide DC power conversion with near ideal efficiency in systems that combine operating at voltages in excess of 500 V with frequencies higher than 1 MHz. This is a major impediment, as such conditions are desired in many applications, including: motor drives for automotive and industrial power supplies; power units in electric vehicles (they are inserted between either the charging unit and the battery, or the battery and the motor); photovoltaic inverters; data centres; and telecom power supplies.

Fortunately, there is a compelling alternative to silicon: the GaN HEMT. It's ideal for power switching, thanks to its capability to handle high voltages and high current densities, and its fast switching speeds.Thanks to these merits, analysts are tipping this device to generate billion-dollar sales by the middle of the next decade.

However, that's not to say that this device is faultless. It has downsides that are delaying its entry to market year after year. While no one doubts its attractive properties, it is not getting traction in markets with wide consumer bases, such as the automotive industry, even though these sectors have an urgent need for the performance it offers.

There are, in fact, two obstacles in the way of the commercial success of the GaN HEMT: its cost and its reliability.

Our team at the IMS CHIPS, has taken a close look at these issues by undertaking a very thorough investigation of the capabilities and weaknesses of the GaN HEMT. One of the key questions that we have investigated is whether this device can have more commercial success when it is formed on silicon, or on a native substrate. Read on to discover our conclusions.

Issues of cost"¦

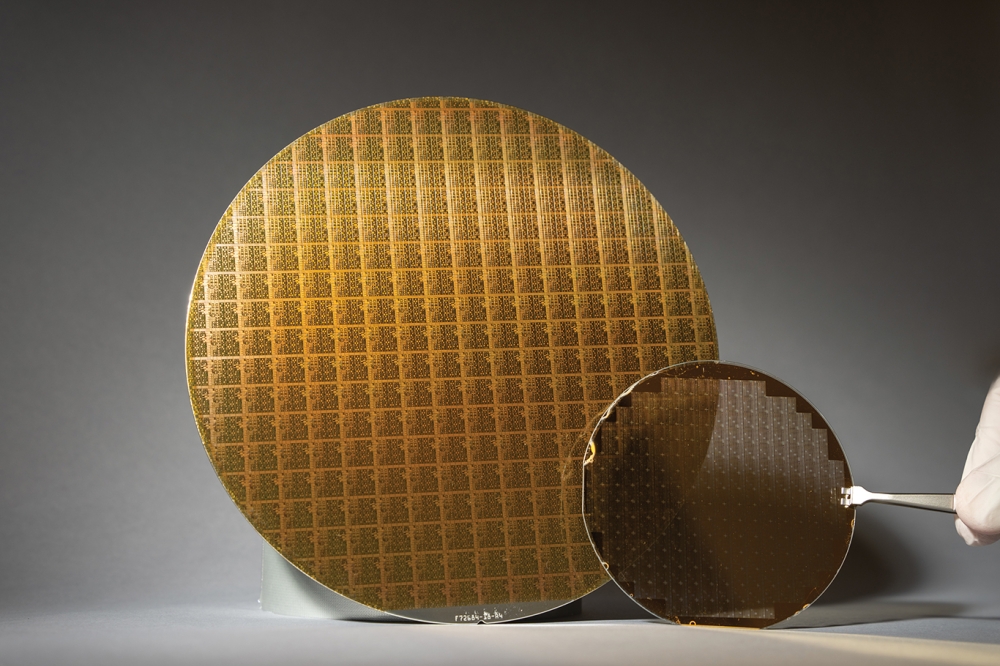

If GaN HEMTs have a reputation for their high-cost, this can be traced to their production on small diameter, expensive substrates, such as SiC. Addressing this concern are large diameter silicon substrates, which are now commercially available through epiwafer suppliers. This material is of sufficient quality to enable high-voltage operation, and it can be processed in already established silicon lines in a CMOS-compatible fashion (see Figure 1 for an image of a 6-inch GaN-on-silicon wafer, similar to what is now routinely processed in our CMOS-line). Anyone using this approach slashes the cost of single die, because GaN can be processed side-by-side with CMOS silicon. No major investment in a separate GaN line is needed.

Figure 1. The 6-inch GaN-silicon wafer (left) can make GaN power devices cost effective, but reliability is attained only by using GaN-on-bulk-GaN wafers, such as the 2-inch wafer shown (right).

However, even with these advances, GaN HEMTs are pricey. The cost of the bare wafer ranges from €2000 to €5000, due primarily to the cost of GaN epitaxy. Growing GaN on silicon is not easy, with a multi-layer stack needed to mitigate the thermal and lattice mismatch between cubic silicon and hexagonal GaN (as depicted in Figure 2). What's more, a relatively thick compensated isolation buffer layer is needed to shield the high voltage from the conductive silicon substrate.

Even with a carefully chosen epistructure, a GaN-on-silicon wafer suffers from high residual stress and large wafer bow. This impacts yield, because it increases the probability of wafer cracking during processing. Devices are also impaired by charge trapping and inefficient thermal dissipation. This stems from the existence of so many different layers and interfaces, and the high defect density, which is of the order of 2x109 cm-2.

Figure 2. Many stress and compensation layers are needed to enable the production of high-voltage GaN HEMTs on silicon substrates. The epitaxial complexity is much reduced with sapphire and bulk GaN substrates.

"¦ and reliability

Operation of the GaN HEMT hinges on a difference in the polarisation between the top layer, which is typically an AlGaN barrier, and the bottom buffer layer, typically GaN. If charges are trapped, this produces an uncontrolled and dynamic imbalance, and ultimately degrades device reliability. Operation of the device leads to a decrease in the channel density "“ often described as an increase in the dynamic on-resistance "“ and an accumulated increase in leakage current, which causes unpredictable device behaviour.

There are implications of this decline in performance for the surrounding control electronics. The worst case scenario is a sudden, catastrophic device or circuit failure.

So, in short, GaN-on-silicon has the potential to be highly cost-effective "“ but it also has some serious flaws, in terms of reliability and thermal management.

Figure 3. Defect mapping on a commercial GaN-on-silicon wafer (left), and the resulting device performance wafer map (right). Here the red marked dies totally failed, while some are below the designed specification. However, most of the die pass the test criteria (blue coloured die).

For our investigation, we could have taken into account the limitations of the GaN-on-silicon wafers while estimating yield and final die cost. But this is far from easy, partly because there are no strict epiwafer standards. What happens in practice is that different suppliers take different approaches, depending on their choices for epitaxial equipment and silicon substrates, to produce epiwafers with the same design.

To enable standardization of the epitaxial process, there is a need for a statistical approach that correlates the general causes for defect generation to the growth technology. This is the track that we are pursuing in partnership with leading reliability and modelling partners. GaN-on-silicon wafers from different wafer suppliers are characterized structurally and electrically, with the statistical results correlated with the common epitaxial steps employed by each supplier.

We process our wafers with our "˜fast loop GaN process'. It forms GaN devices using the fewest and least interfering fabrication steps "“ that is, without inducing any degradation to the material quality during device processing. Although this approach is not capable of producing as a complex structure as a CMOS-based process, it is the best choice for material characterization purposes. That's because it provides fast, comprehensive analysis of the wafer's quality to the wafer supplier. The turnaround time is between two and four weeks, depending on the extensiveness of characterization and reporting.

The characterization that we can provide ranges from DC measurements to reliability analysis. This can be undertaken on full or partial wafers.

An example of our work is obtaining a defect map on an unprocessed, 6-inch, GaN-on-silicon wafer (see Figure 3). Using our fast-loop process, we can quickly correlate the electrical results to the physical state of the wafer. Adopting this approach in a wider and statistical manner should enable a common consensus on the most suitable way forward for epitaxy.

It is clear that exploitation of the lower costs associated with GaN-on-silicon hinges on greater standardisation of these epiwafers, and a more thorough investigation of approaches that can mitigate the reliability issues arising from epitaxy. However, if the reliability issue is to be fundamentally solved, defects and trapping centres will have to be eliminated "“ and this appears to only be possible by switching to homo-epitaxy of GaN HEMTs, using insulating bulk GaN substrates.

There are many merits associated with the use of native substrates: there is no need for stress relief and compensation layers; and the defect density plummets, falling from either 2 x 109 cm-2 for a commercially available GaN-on-silicon wafer, or 9 x 108 cm-2 for GaN grown on sapphire, to less than 1 x 106 cm-2.

To highlight the improvements in reliability that stem from a switch from a foreign substrate to a native one, we have characterised GaN-on-GaN, GaN-on-silicon and GaN-on-sapphire wafers using our fast loop process. Note that although compensation layers are not needed for GaN-on-sapphire and GaN-on-GaN, they were added to enable direct correlation of reliability and defect density. The benefits of a lower defect density on reliability are abundantly clear, with leakage current falling by three orders of magnitude when a foreign substrate is replaced with a native one (see Figure 4 that shows plots of the evolution of the leakage current with voltage, when the device is in the off-state.).

Figure 4. GaN-on-bulk-GaN HEMTs show inherently lower leakage than those based on GaN-on-silicon and GaN-on-sapphire.

By monitoring the device current immediately after the off-state, it is possible to infer trapping effects due to defects. We have investigated this, conducting measurements after different off-state voltages (see Figure 5). This shows that regardless of substrate, trapping increases with the off-state voltage. However, the extent of this trapping varies, with GaN-on-GaN devices the least affected, and those with silicon and sapphire foundations loosing almost half their on-state current. For GaN-on-GaN devices, most of the trapping is in the compensation layer. As stated already, this is not needed, and without it trapping should be greatly reduced.

When the device is on, it is conducting current. This causes it to self-heat, and the longer it is on, the greater the reduction in current (see Figure 6).

Armed with a native substrate, the GaN HEMT is relatively immune from self-heating effects. Thermal effects are far worse when this transistor is grown on sapphire, because this substrate has a poor thermal conductivity, hampering thermal dissipation. At first glance, silicon should be a good choice, due to a thermal conductivity that exceeds that of GaN. However, with this pairing, thermal power dissipation is held back by highly defective nucleation and compensation multi-layers.

So, judged in terms of reliability, the best foundation for the GaN HEMT is a bulk GaN substrate. But when this is viewed from a commercial perspective, it has some major drawbacks: it is pricey, small in size, and there is limited availability of the insulating form that is needed for high-voltage devices.

Figure 5. GaN-on-silicon HEMTs suffer from stronger charge trapping effects than those formed on bulk GaN.

Two options for manufacturing bulk GaN are ammonothermal growth and HVPE. The former yields the best quality material, which is semi-insulating. However, crystal growth conditions are difficult to control, leading to substrates that are too expensive, too variable in quality from vendor to vendor, and limited to a diameter of up to 2-inch. What's more, it appears that high-volume production is not yet possible.

Many of these issues are addressed with the HVPE approach. It involves the growth of GaN on sapphire until it is thick enough to yield a high-quality, defect-free layer. At that point, the layer is removed from sapphire. Substrates are then formed, with processing producing high-quality surfaces.

Figure 6. The thermal dissipation capability of the bulk GaN substrate allows much reduced self-heating. Although silicon has a higher thermal conductivity than GaN, the multi-layers needed for stress compensation act as a thermal bottle neck.

Thanks to growth rates as high as 200 mm/hour "“ this is seven times that of the ammonothermal approach "“ several substrate manufacturers are using this approach. Their products are offered in various grades, in terms of crystalline quality and insulation, and although this method requires separation and finishing steps, the size of the substrate is limited only by the size of the carrier sapphire wafer. This form of substrate, which we have used in our investigation, is employed for the manufacture of blue lasers and ultra-high-power LEDs. If this optoelectronics sector continues to grow, availability of such wafers should increase, leading to a reduction in their cost.

Today, the manufacturers of GaN HEMTs have to choose between a lower-cost substrate that compromises reliability, and one that yields a better, but more expensive device. One implication of this is that for the next few years, GaN-on-silicon HEMTs may only enjoy commercial success in applications where the operating voltage is far below the capability of GaN, because this reduces reliability issues. Meanwhile, HEMTs produced on a native substrate can demonstrate the full capability of this device in power applications, where they will enable highly efficient, compact size power electronics. However, due to the high cost of these transistors, they will only serve in niche applications.

Ideally, this state-of-affairs will change when larger, lower-cost bulk GaN substrates are available. This will not happen overnight, but while we wait, we hope for a gradual reduction in cost. This may occur through the introduction of substrate transfer methods, where the active layer of several 2-inch bulk GaN wafers is transferred to a carrier substrate, such as 8-inch silicon, and the remaining template is reconditioned and reused. We are active in this, working with a leading epitaxy partner. Together, we plan to produce material by this approach within two years, with the aim of increasing the commercial appeal of the GaN-on-GaN HEMT.