IRPS: Gaining greater insight into the GaN HEMT

A more comprehensive understanding and evaluation of the GaN HEMT comes from a rigorous model of how it is deployed and new approaches to scrutinise this device.

BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

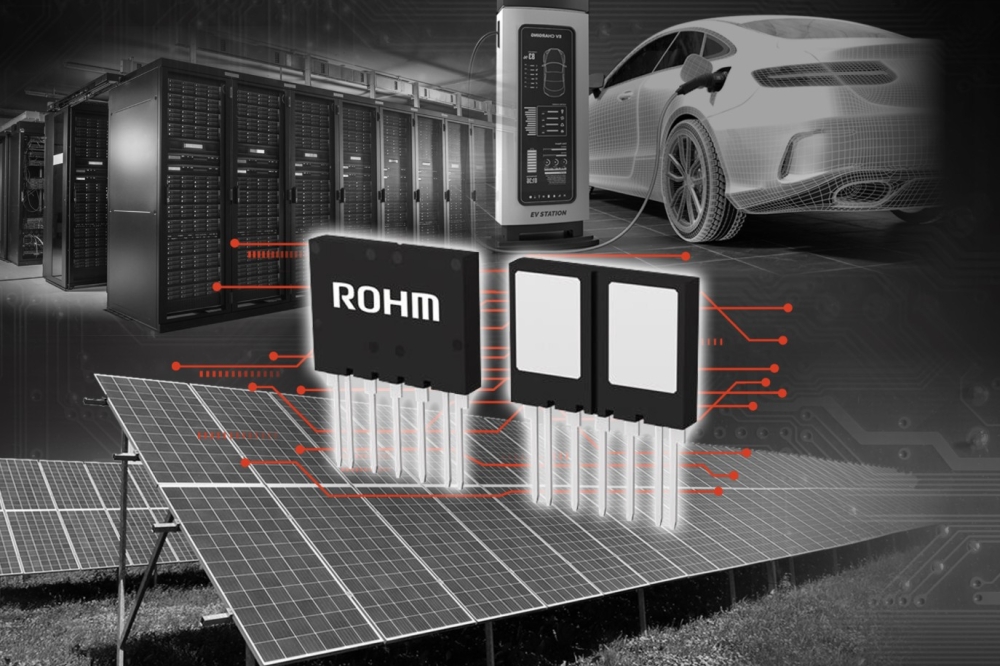

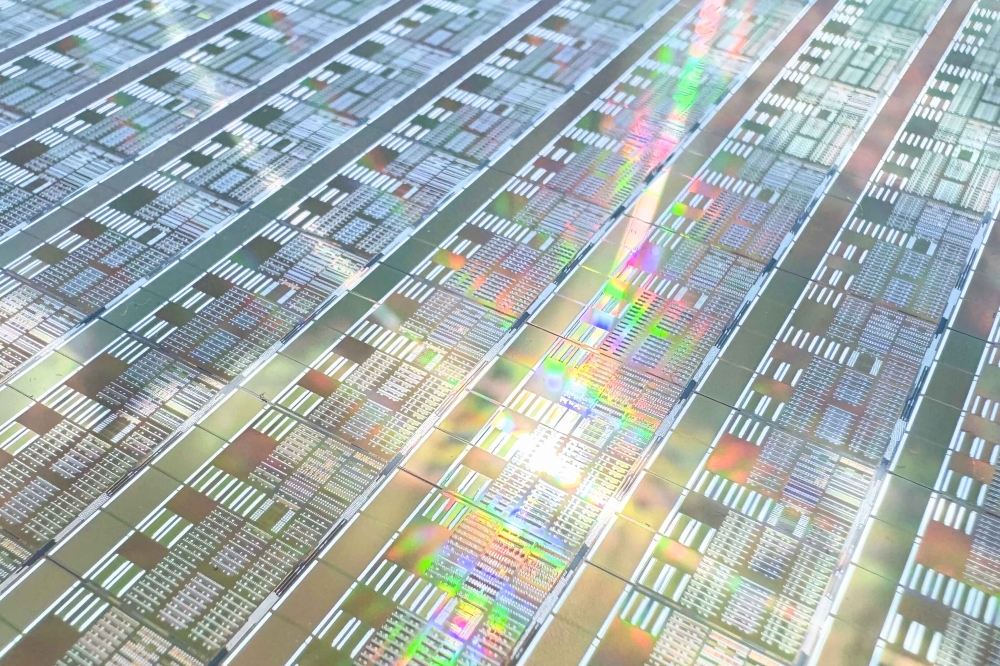

When deployed in power electronics, the GaN HEMT delivers a great deal of bang per buck. Its strong performance stems from a number of attractive attributes, including a capability to withstand very high electric fields, an excellent electron mobility, and a high operating frequency. These strengths are realised alongside a competitive cost, thanks in part to the growth of GaN on large-diameter silicon wafers that can be processed in established lines.

The compelling performance of the GaN HEMT is driving its uptake in ever more applications. It’s first taste of significant success came from its incorporation in fast-chargers for mobile devices. And over the coming years, shipments will continue to rise as it wins sales in more markets, with deployment forecast in telecommunication and data centre infrastructure, motor drives and inverters for solar panels.

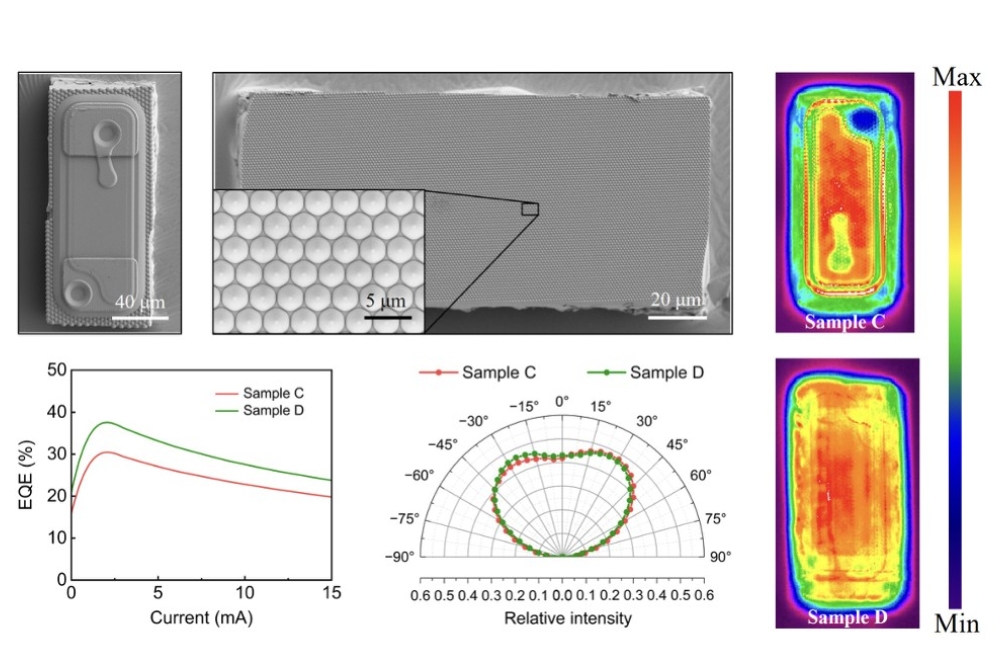

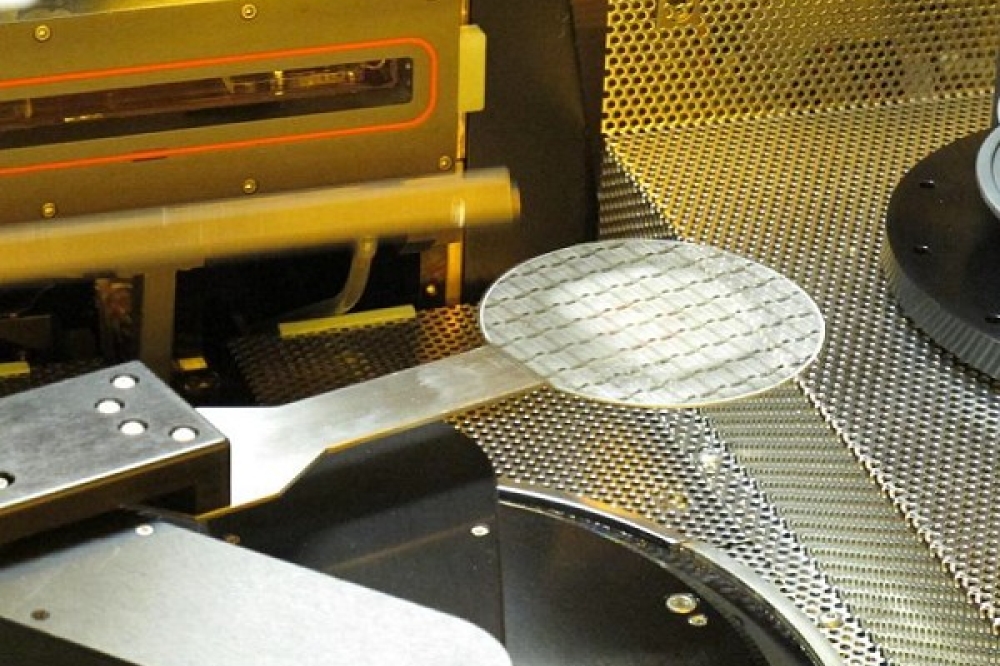

Figure 1. The set-up used by the University of Padova, in partnership with BelGaN, for on-wafer measurements of threshold voltage and on-resistance. This set-up includes an arbitrary waveform generator, two amplifiers that connect the arbitrary waveform generator to the device under test, an oscilloscope to acquire all the signals, and a clamp circuit that is needed to measure the drain voltage, in order to extract the on-resistance of the device.

However, there is still much to do to ensure that the GaN HEMT has long-term, growing success in these markets. As it will be deployed in more demanding applications and undergo a range of stresses, including those that come from hard switching and ringing, it is vital to understand the level of reliability it offers in these situations. In addition, the GaN HEMT is still a work in progress, so it’s important to gain a deeper understanding of its weaknesses – they include a trapping of carriers, which can lead to an increase in on-resistance and a shift in threshold voltage. In some cases, measurements are needed on production devices, ideally undertaken on-wafer, as this saves time and money.

The good news is that progress is being made on all these fronts, with gains reported at this year’s International Reliability Physics Symposium (IRPS), which took place on 14-18 April in Dallas, Texas. At this conference Sandeep Bahl from Texas Instruments outlined a more robust approach to assessing GaN reliability in various power-supply applications; on-wafer approaches to measure on-resistance, threshold voltage and degradation that have been pioneered by the University of Padova, STMicroelectronics and BelGaN, were described by two spokesmen from the university; and Yu-Shan Lin from TSMC detailed the impact of different processes on trapping in field plates.

Figure 2. There are relatively small changes in the on-resistance (RON) and the threshold voltage (VTH) during soft-switching.

Reliability in the field

To help ensure that power electronics offers sufficient reliability in a range of applications, standards exist for assessing device performance. This is not a new innovation, having been established for silicon technologies several decades ago. There are documents from the mid-1990s specifying the methodology to evaluate this device, consider electrostatic discharge, and to put this package through its paces. Such standards are accompanied by documentation for accelerated test-to-failure, used to calculate lifetimes from relevant failure mechanisms.

More recently, standards have expanded to GaN HEMTs. The guideline JEP 180, published in 2020, offers guidance for calculating the switching lifetime from accelerated lifetime testing. Bahl highlighted this documentation when describing what is claimed to be the first generalised approach for determining the hard-switching lifetime of a GaN transistor.

“We first use a test-vehicle circuit appropriate for accelerating the desired switching-stress type, which was hard switching,” remarked Bahl. “We then ran accelerated lifetime testing on a TI GaN part, generated a model and calculated the switching lifetime.”

Figure 3. Hard switching leads to significant changes in on-resistance (RON) and the threshold voltage (VTH).

According to Bahl, there are three main challenges when determining the switching lifetime: the complexity of the switching transition, which involves voltages, currents, temperatures, duty cycles, frequencies and slew rates; dependence of the stress on the application circuit; and the lack of a broad modelling approach.

Bahl explained that it is desirable to have a test vehicle circuit for the stress test, and for the switching lifetime to be calculated for a broad application use: “This would allow the use of a test wafer circuit suitable for accelerating the desired failure modes. This is an important factor, because regular application boards are typically not suitable for high acceleration, and may produce false failures, or incorrectly accelerate the failure mode desired.”

To evaluate lifetime, Bahl and co-workers have used a boost converter circuit, with the output tied back to the input. This provides a hard-switching stress to the device.

Claiming to break new ground, the team from TI has determined the switching stress by integrating the switching waveform, including wearout acceleration factors. This approach is said to capture the complexity of the switching waveform. To provide a generalised methodology, Bahl and co-workers have also considered the switching stress rate, which accounts for the temperature, duty cycle, frequency and the switching stress per transition. “An important advantage of this approach is that is allows the use of conventional reliability acceleration functions,” added Bahl.

Figure 4. The set-up used by the University of Padova, in partnership with STMicroelectronics, for on-wafer measurements of the degradation of GaN HEMTs.

According to him, one advantage of the switching stress calculations is that they can be applied to any switching waveform, regardless of whether it is measured or simulated. Using both simulated and measured waveforms, the team have determined switching lifetimes for a TI part. This suggests a lifetime of more than 1 billion years for 400 V, 8 A hard-switching at 100 kHz.

“Note that the model is for hard failure due to hard switching, since that was the type of stress accelerated,” remarked Bahl. “Other types of stress would be considered either independently or cumulatively, depending on whether the same failure mode is exercised.”

Passivation and layout

Hard-switching conditions were also employed during on-wafer measurements by the University of Padova and BalGaN, a collaboration that considered the impact of passivation and gate layout on both the on-resistance and the threshold voltage.

Before detailing this work at IRPS, Davide Favero from the University of Padova discussed some of the origins of the weaknesses in GaN HEMTs.

Favero remarked: “Due to the lower maturity level of the technology of p-GaN HEMTs compared to silicon carbide MOSFETs, these devices may suffer from instabilities, concerning both threshold voltage and on-resistance.”

He pointed out that there can be a threshold voltage instability induced by the gate bias, primarily due to either the trapping of electrons or holes, or the injection of holes from the gate contact. A drain bias induced threshold voltage instability may also arise, associated with hole deficiency.

Figure 5. On-wafer measurements of degradation in 650 V p-GaN lateral GaN-on-silicon HEMTs involve on-resistance estimation pulses and stress pulses.

Gate and drain bias can also influence the dynamic on-resistance, according to Favero: “The most common instabilities are due to drain bias, but in literature it was shown that gate bias can induce an increase in on-resistance, because of hole traps in the AlGaN.”

Under drain bias, the dynamic on-resistance can both increase and decrease. Increases can come from an injection of electrons from the substrate towards the buffer, leading to trapping; and ionisation of buffer acceptors, usually carbon, leading to a redistribution of charges in the buffer. It is also possible to have positive charges generated inside the buffer, causing a decrease in on-resistance. However, through an optimised process, it is possible to ensure a stable dynamic on-resistance.

According to Favero, one significant concern for the GaN HEMT is its operation under hard switching, which enhances the trapping process through the presence of hot electrons. Trapping occurs at the gate stack, and also in the access region, where it occurs at the interface between AlGaN and the passivation layer.

“These hot electrons may lead to an increase in the on-resistance, but also to an increase in the threshold voltage, because of trapping of electrons in the gate stack”, remarked Favero, before adding: “I believe it is of crucial importance to be able to distinguish between an increase in on-resistance due to an increase of the resistivity of the channel in the access region, and an increase in the on-resistance that is due to an increase in the threshold voltage.”

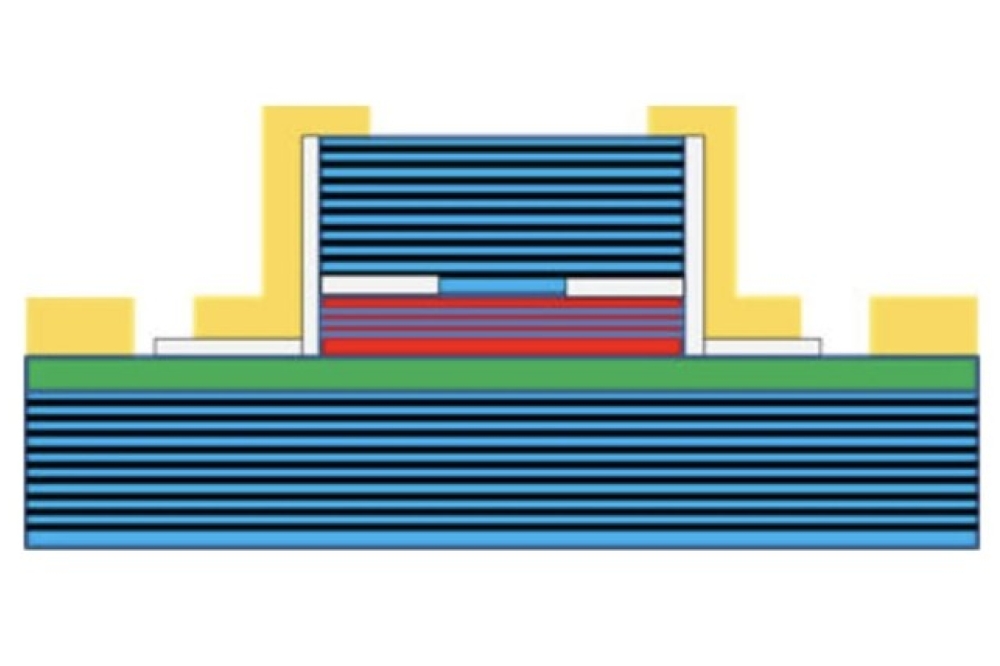

To distinguish between these two causes, Favero and co-workers use a custom set-up, involving commercial instruments and homemade circuits (see Figure 1). This highly flexible approach offers complete control of the waveforms, and enables measurements in the microsecond range.

Using this set-up, the researchers have subjected devices to hard switching, using a range of pulsed currents and voltages. Hard-switching conditions, which are kept constant through judicious selection of the applied voltage waveforms, enable extraction of values for on-resistance and threshold voltage.

Favero and colleagues have used this approach to assess a portfolio of HEMTs with a p-GaN gate, fabricated on a 150 mm silicon substrate. Within this family of devices are transistors with shorter and longer gate lengths, and three forms of passivation.

Efforts began by assessing devices under soft switching, a condition where the architecture of the field plates and passivation do not have a significant impact on HEMT performance. Increases in the drain bias led to an increase in threshold voltage, due to hole deficiency (see Figure 2). There is also a shift in threshold voltage when applying 5 V to the gate before the measurement – this shift is due to electron trapping in the barrier.

There is minimal change in the dynamic on-resistance with drain bias, due to a balance between different mechanisms occurring in the buffer, such as the ionisation of carbon dopants and the generation of positive charges.

Under hard switching, there are significant shifts in both on-resistance and threshold voltage, with the greatest changes occurring when the drain voltage increases from 0 V to 100 V (see Figure 3).

The team have studied the impact of their three different passivation processes using drain voltages between 0 V and 125 V. Differences in processes did not lead to significant variation in threshold voltage, but did lead to marked differences in on-resistance.

Figure 6. Trapping, probably in the buffer, is the main cause of on-resistance degradation in 650 V p-GaN lateral GaN-on-silicon HEMTs.

“Because of difference passivation, we have a different amount of defect states at the passivation-AlGaN interface that results in different on-resistance increases,” explained Favero, who added that the process is completely recoverable.

He and his co-workers have also found that shorter field plates lead to a lower increase in on-resistance with voltage. According to simulations, the shorter field plate offers a better performance, thanks to a reduction in the peak electric field. Meanwhile, the threshold voltage is not affected significantly by changes to the field geometry.

Delving into dynamic on-resistance

On-wafer measurements of the on-resistance have also been carried out by Favero’s colleague, Micro Boito, who reported results on an investigation by the University of Padova, in partnership with STMicrolectronics. This effort focused on studying the degradation processes associated with dynamic operation of GaN HEMTs.

Boito argued that there are two leading tests or validating GaN HEMTs. One is the dynamic high-temperature operation lifetime test, which runs for 1,000 hours under specified conditions that represent all typical applications. “This usually follows the JEDEC guidelines,” remarked Boito. He explained that the other test is the switching advanced life-time test – this aims to extract the main degradation mechanisms by applying more stressful conditions for a shorter period of time.

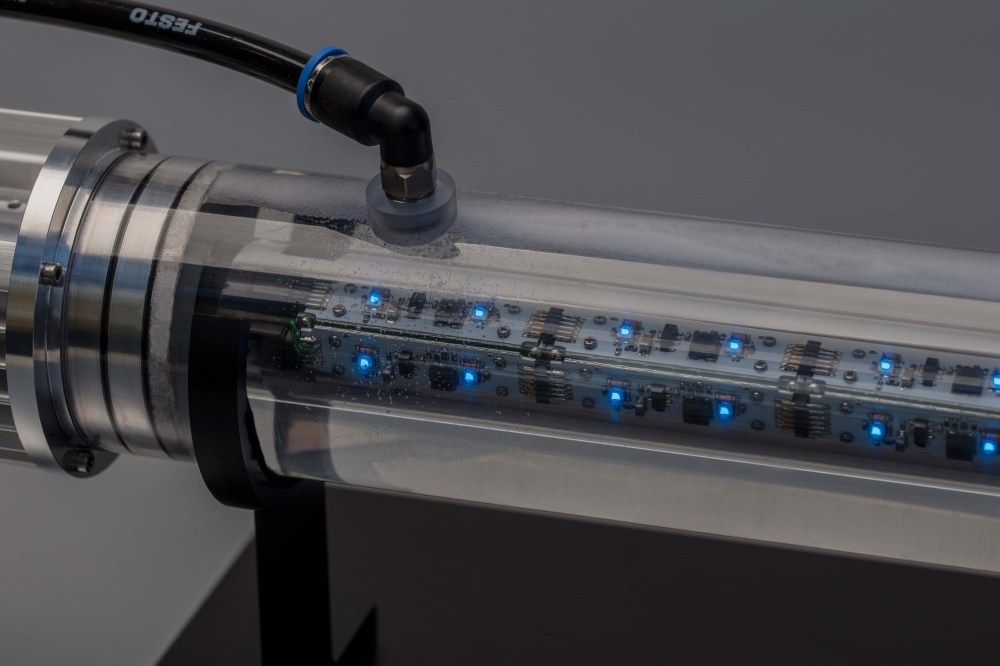

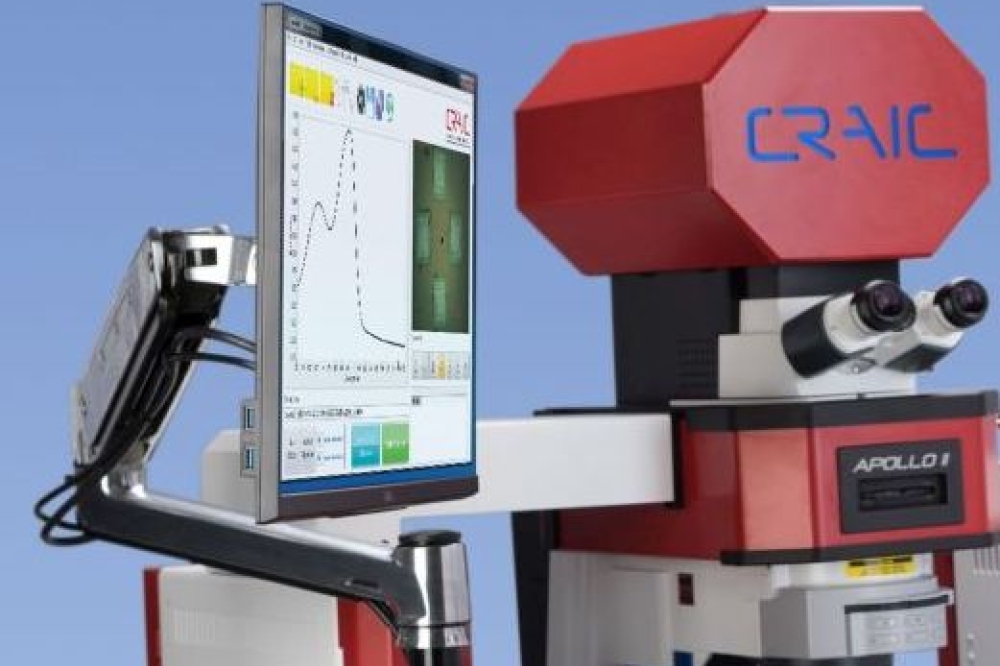

The novelty of the work of Boito and co-workers is that it offers a new way to conduct on-wafer tests (see Figure 4). Strengths of this latest approach are: the introduction of a current-sensing circuit, to evaluate the drain-current waveform during switching; and due to subjecting the drain current waveform to a large swing, improvements to the voltage sampling resolution, by adding a fast clamp circuit that limits the applied voltage to the oscilloscope channel. The team’s set up allows fine tuning of the stress conditions from soft to hard switching by adjusting the overlap and the rise and fall times between the gate and drain signals.

Figure 7. Step stress measurements from 100 V to 600 V have uncovered two different trapping mechanisms in 650 V p-GaN lateral GaN-on-silicon HEMTs (top). Processes that impact the two-dimensional electron gas can account for changes in the on-resistance (bottom).

With this set-up the team have monitored the dynamic degradation of state-of-the-art 650 V p-GaN lateral GaN-on-silicon HEMTs under hard switching and off-state stress. This work involves using two pulses: an on-resistance estimation pulse that determines the resistance via ohm’s law, and a stress pulse. On-resistance estimation pulses are applied on a logarithmic time scale, with the stress pulses deployed between each of them (see Figure 5).

To distinguish between permanent and recoverable degradation, Boito and co-workers illuminate these samples with a 365 nm source. This excitation liberates traps within the device, thereby identifying recoverable degradation.

The team have undertaken voltage-step stress measurements on 10 devices, with an off-state voltage rising from 100 V to 520 V, using what is described as a cross-over level of 30 percent – that’s the overlap between the gate and drain voltages. For this investigation, the switching frequency is 20 kHz.

A degradation in on-resistance is seen in these measurements, with an onset that occurs earlier at a higher off-state voltage (see Figure 6). However, for all 10 devices, the unwanted increase in

on-resistance can be recovered by exposure to UV light. Based on this finding, Boito claimed that trapping, probably in the buffer, is the primary cause of on-resistance degradation. Subsequent temperature-dependent measurements supported this suggestion of trapping in the buffer.

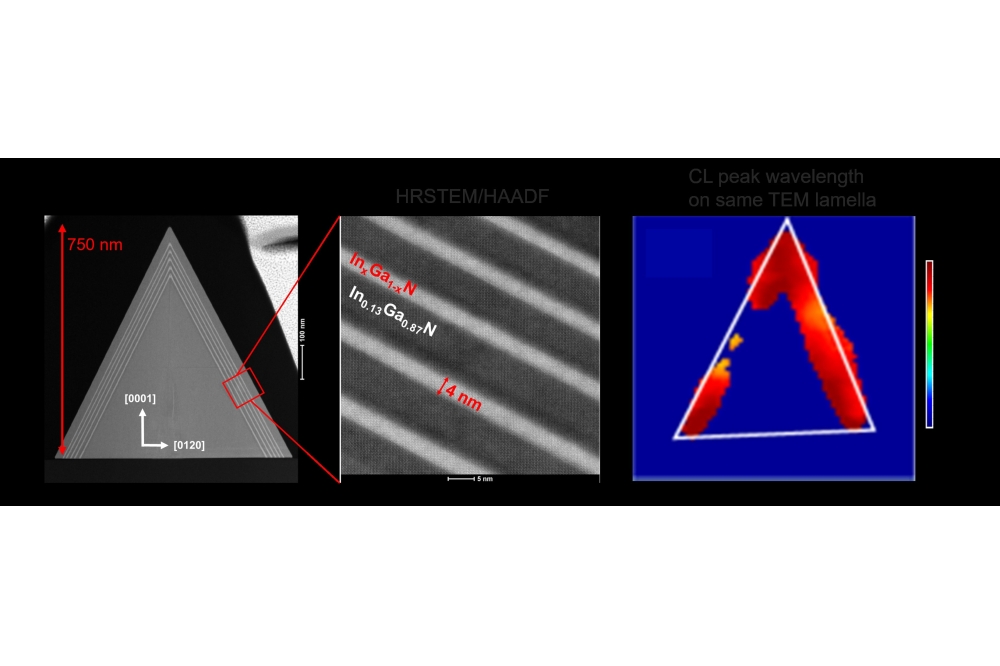

Boito and colleagues have also collected off-state stress, so they can separate the impact of hard-switching from buffer trapping. Step stress measurements from 100 V to 600 V have uncovered two different trapping mechanisms: initially surface trapping at short stress times, associated with surface traps; and later on an exponential fall in in on-resistance, due to buffer traps (see Figure 7).

Modelling by the team explains both trapping mechanisms. The surface trapping comes from a high polarisation during the off-state that causes a leakage current, leading to ionisation of carbon acceptors in the carbon-doped region. A redistribution of the charge with the carbon-doped and unintentionally doped layers follows, causing the depletion of the two-dimensional electron gas, and ultimately a lowering of the drain current and an increase in on-resistance.

Under a longer stress time, there is band bending, due to charge storage in the unintentionally doped and carbon-doped layers that leads to an increase in tunnelling probability. This leads to generation of electron-hole pairs at the interface, and in turn band-to-band tunnelling in the unintentionally doped GaN layer, alongside the generation of positive charge at the bottom of the carbon-doped layer. These processes increase the density of the two-dimensional electron gas, and lower the on-resistance.

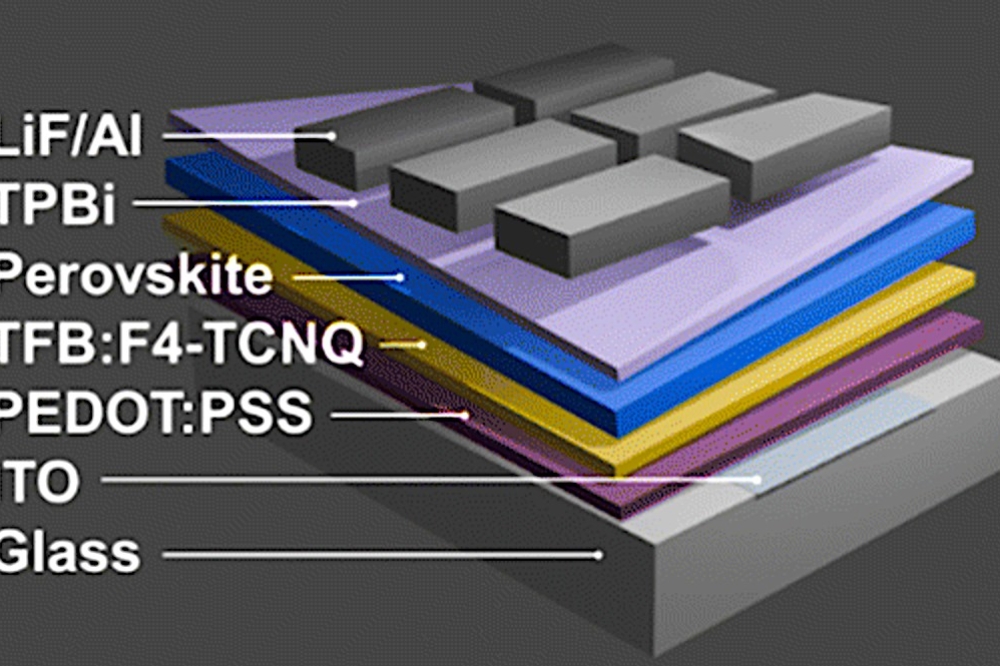

Figure 8. TSMC has studied E-mode 650 V GaN devices, housed in a TO-220 package and having the substrate connected to the source. Process-2 producing a strong polarisation that leads to a higher value for the two-dimensional electron gas.

Analysing traps

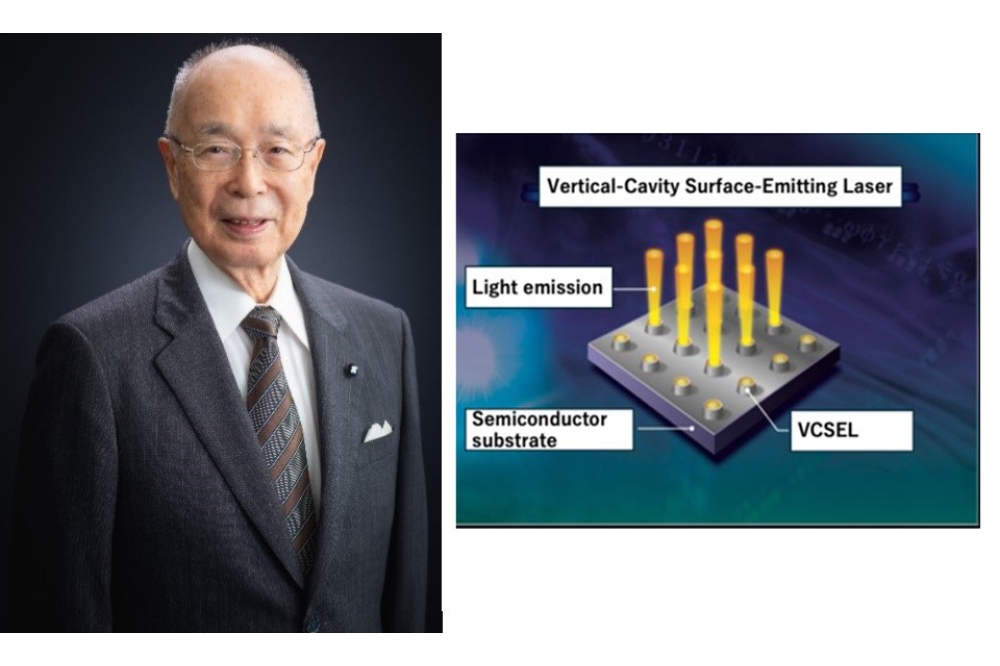

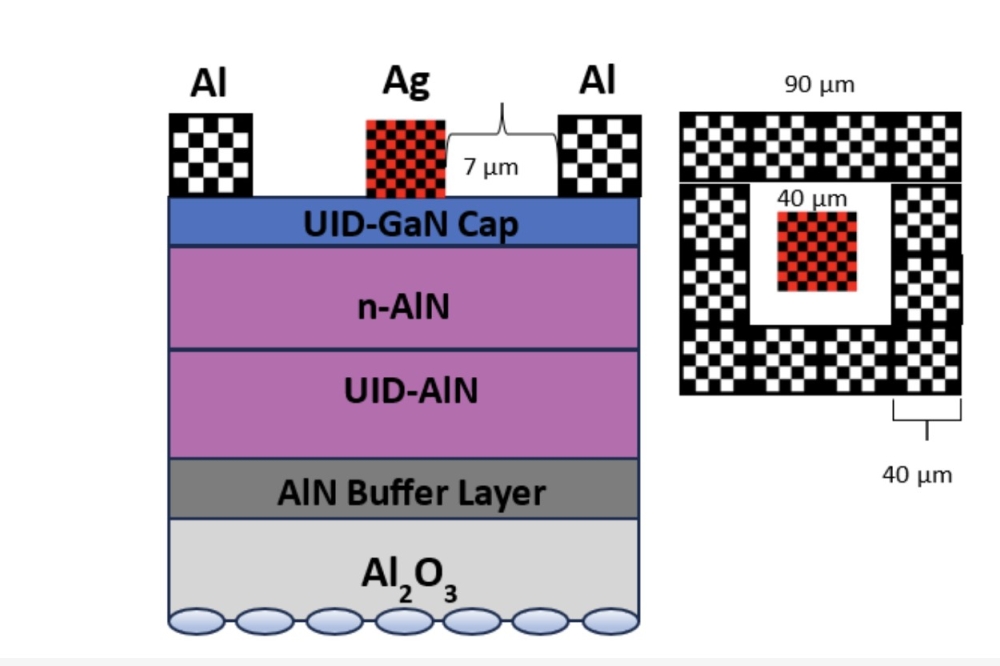

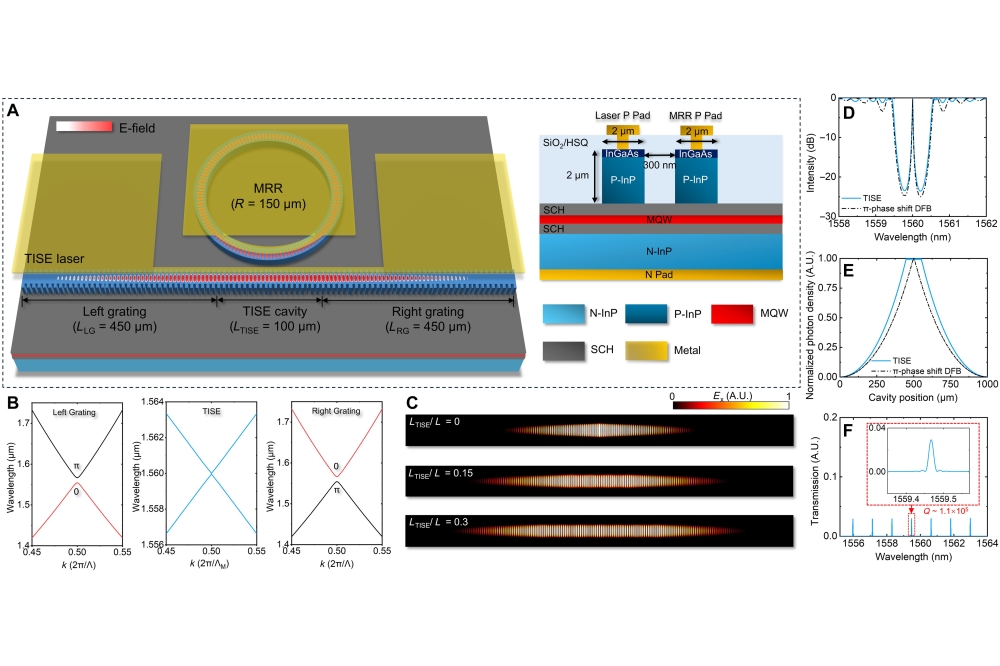

At TSMC, engineers have investigated the correlation between defect-generation regions and field plates using capacitance-voltage analysis at high voltages. This effort, involving HEMTs and reported at IRPS by Yang, targeted improved trapping behaviour through optimisation of the production process.

Yang and her co-workers have investigated 650 V E-mode HEMTs that feature two field plates, have the substrate connected to the source, and are housed in a TO-220 package. HEMTs have been formed using two processes, with what is referred to as Process-2 producing a stronger polarisation that leads to a higher value for the two-dimensional electron gas, and higher on and off currents (see Figure 8).

The team from TSMC have used a Keysight B1505A power device analyser to conduct high-voltage capacitance-voltage measurements of their devices. The goals have been to assess the processes, and to determine which one provides

the best balance between performance and reliability.

To evaluate reliability, Yang and her colleagues undertook high-temperature reverse-bias measurements, employing a gate voltage of 0 V, a drain voltage of 520 V, and an elevated temperature of 150 °C. Over 48 hours the team monitored changes to the linear drain current (see Figure 9).

Figure 9. Engineers at TSMC studied the degradation of the linear drain current by employing a gate voltage of 0 V, a drain voltage of 520 V, and an elevated temperature of 150 °C.

“We found that the [linear drain current] initially improved, due to the accumulation of holes in the buffer, but after 10,000 seconds it started to degrade due to the stress,” remarked Yang. She attributes initial behaviour to the test inducing vertical band bending, which results in a redistribution of electrons and holes in the carbon-doped GaN layer, explaining that electrons are drawn to the channel and collect at the drain, while holes accumulate in the buffer layer. “This accumulation of holes in the buffer layer reduces the on-resistance of the channel and enhances the two-dimensional electron gas,” argued Yang. Both devices were found to have a similar level of enhancement to the linear drain current, implying that the GaN buffer layer is of consistent quality.

Another key finding by the team is that the electron trap that is responsible for the degradation in the linear drain current is located outside the buffer layer.

Support for these inferences comes from capacitance-voltage plots of HEMTs produced by both processes (see Figure 10). The behaviour of the electron trap at the first field plate during capacitance-voltage measurements indicates that the degree of electron trapping near the gate is much greater than the effect of hole trapping. Note that the behaviour at the second field plate is markedly different, dominated by hole trapping.

Also shown in Figure 10 are shifts in the depletion voltage, calculated from capacitance-voltage measurements. This information uncovers both the type of trapping, and its extent – revealed by the degree of shift. Based on these profiles, Yang and co-workers have concluded that: the trap capture caused by process-2 is more stable in the field plate region; the field plate region is more susceptible to electron trapping; and that the electron trap near the gate at the field plate is improved by process-2, based on high-temperature reverse-bias measurements.

“To distinguish the effects of the bulk and dielectric layers, we modified the device design,” explained Yang. This involved connecting the source and gate, while isolating the bulk.

The team used a floating bulk stress to eliminate the impact of the buffer layer, and applied a bulk stress of -650 V to mitigate the effect of the dielectric layers and emphasise the impact of bulk traps.

The key conclusion from this experiment is that holes in the bulk stress enhance the linear drain current. Based on this observation, it’s argued that in addition to electron trapping, holes that accumulate in the carbon-doped GaN layer play an important role during high-temperature reverse-bias tests.

Figure 10. TSMS’s capacitance-voltage plots on the HEMTs taken during high-temperature reverse-bias stress offer insight into carrier dynamics.

In addition, the team have carried out capacitance-voltage measurements after subjecting devices to 48 hours at a high temperature under reverse bias. This investigation revealed that the trap density is significantly reduced after the application of a high temperature and reverse bias, with the greatest gains occurring in the field plate region located near the gate. This led Yang and co-workers to speculate that improving material quality can cut the concentration of native defects, resulting in a lower trapping density.

“We hope that our findings will inspire further research in the field and contribute to the development of more efficient and reliable power devices,” added Yang.

These sentiments will be held by all those at IRPS, with their progress helping to underpin the production of more competitive, higher-performance power devices that will play a key role in helping to address climate change.