Bipolar p-FETs enable all-GaN power integration

Bipolar transport overcomes the inherent barriers of GaN p-FETs to pave the way to higher current densities.

BY MENGYUAN HUA FROM SOUTHERN UNIVERSITY OF SCIENCE AND TECHNOLOGY

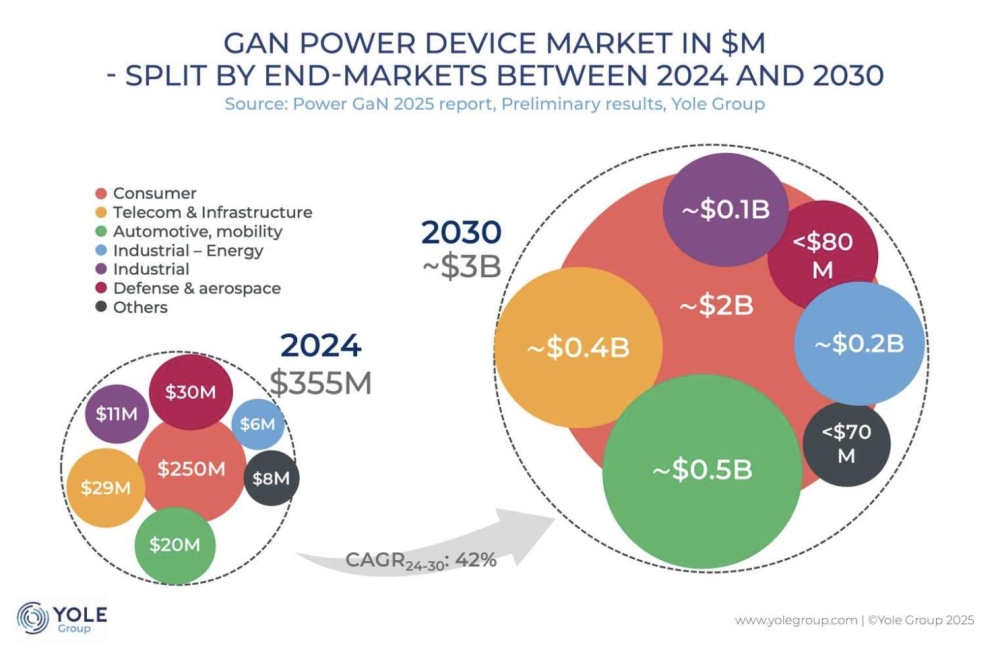

GaN power devices have many attributes. They are renowned for their exceptional switching efficiency and high power density, strengths that are driving the development of miniaturised, energy-saving power systems. Thanks to a wide bandgap and stable material properties, GaN-based power devices are also capable of maintaining a good performance in challenging environments, such as extreme temperatures and irradiation conditions. And in addition to these capabilities, GaN power devices are revolutionising power systems towards higher levels of integration and intelligence. Given all this, it’s of no surprise that GaN-based HEMTs have rapidly surpassed traditional silicon devices to play an indispensable role in a number of fields, ranging from consumer electronics to industrial power supplies.

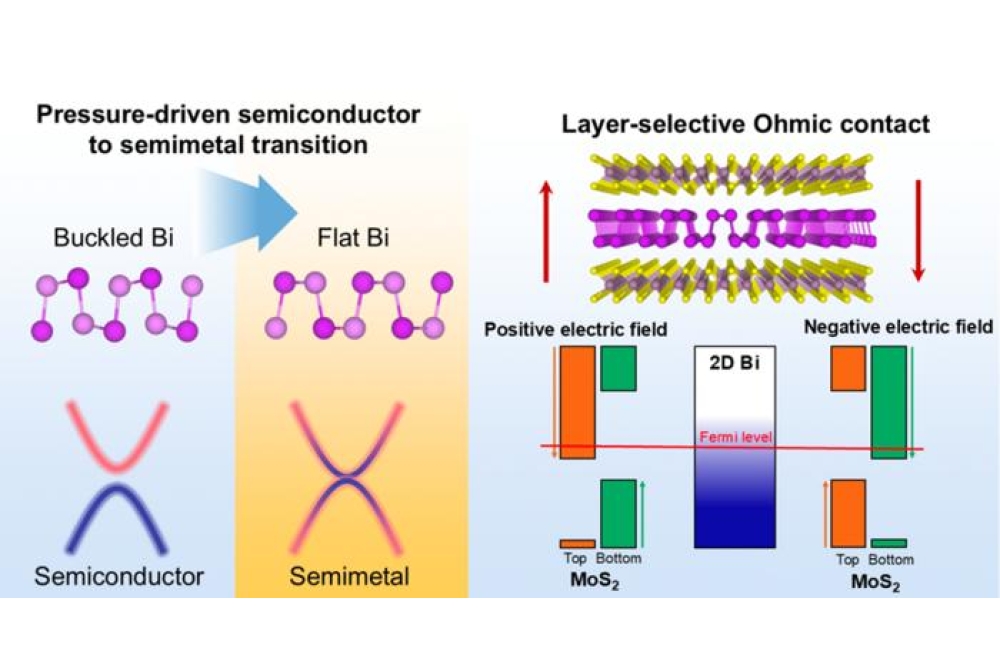

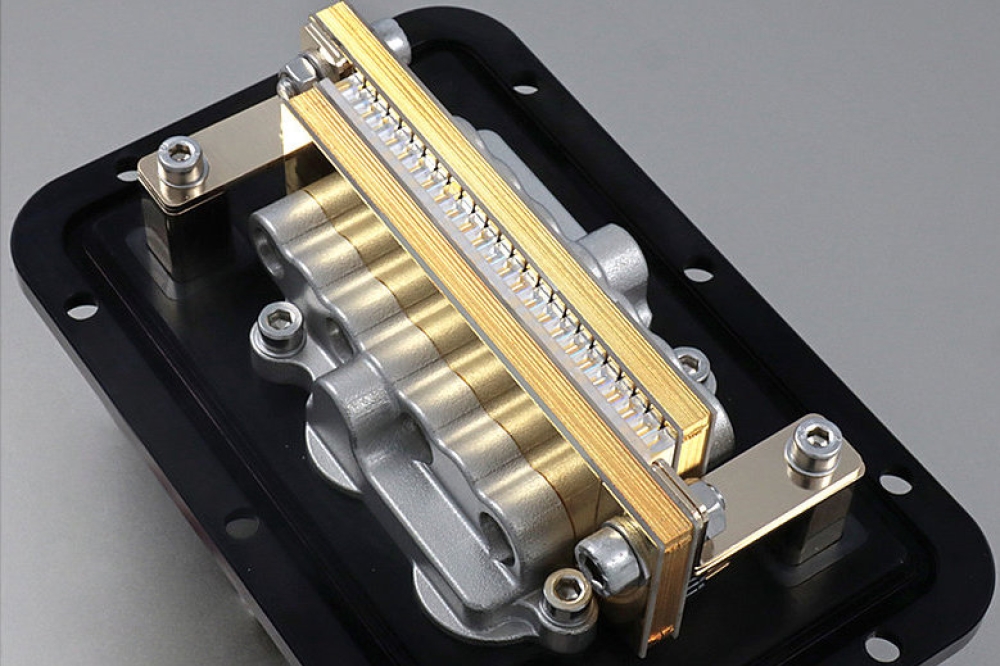

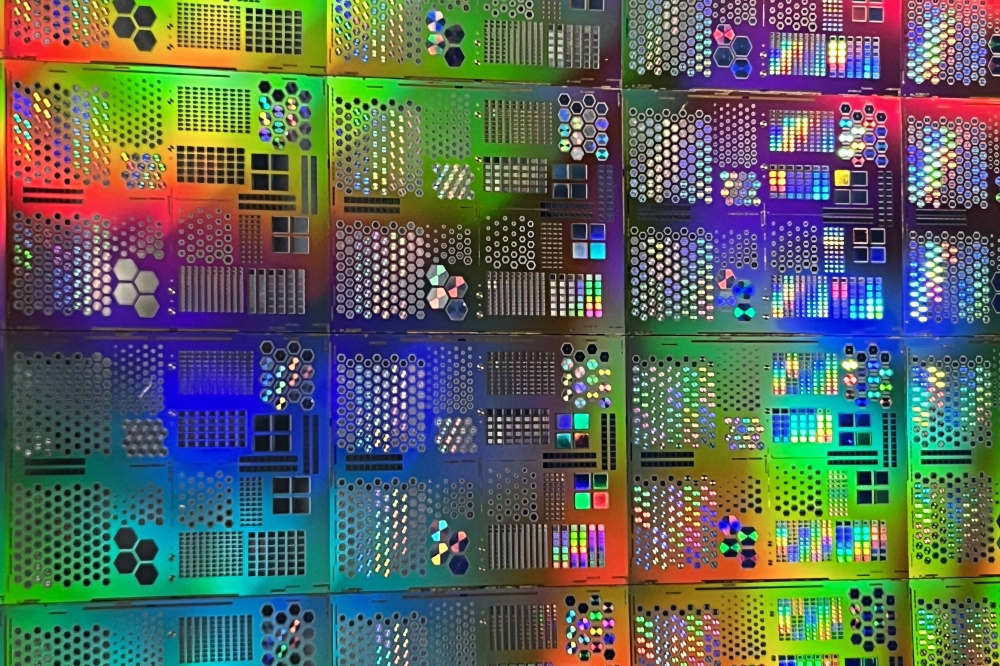

Figure 1. A promising option for GaN integration is the combination of the p-GaN gate HEMT and the bipolar p-FET.

However, while much progress has been made to date, there is still much more to do. In this regard, one important area for improvement is the GaN power IC – today there is a significant challenge in realising the seamless integration of power devices with low-voltage peripheral circuits. In the latest approaches to hybrid integration, the silicon-based circuits that are used for driving, sensing and protecting functions, are integrated with GaN power devices through packaging. This results in non-negligible parasitic inductance, which can lead to gate ringing, particularly during high-power fast-switching transients. Two downsides of this are a limited switching speed and a compromised system reliability. What’s more, the silicon devices in these hybrid designs fail to handle extreme environments as well as GaN devices, narrowing the application scope. Consequently, moving to an all-GaN integration strategy has much appeal, including liberation from parasitic issues and the constraints of silicon-based devices, as well as the opportunity to unleash the full potential of GaN power ICs.

There are several straightforward approaches for all-GaN integration, such as leveraging established n-channel device technology, resistor-transistor logic and direct-coupled FET logic. However, all these methods are impaired by excessive power consumption, due to a significant static current that diminishes the efficiency of the power IC and necessitates enhanced heat dissipation strategies.

A promising solution to effectively blocking the static current is the GaN-based complementary logic IC, incorporating both the p-FET and the n-FET. In this design, the existing p-GaN layer on the E-mode GaN HEMT platform is used to fabricate the p-FET.

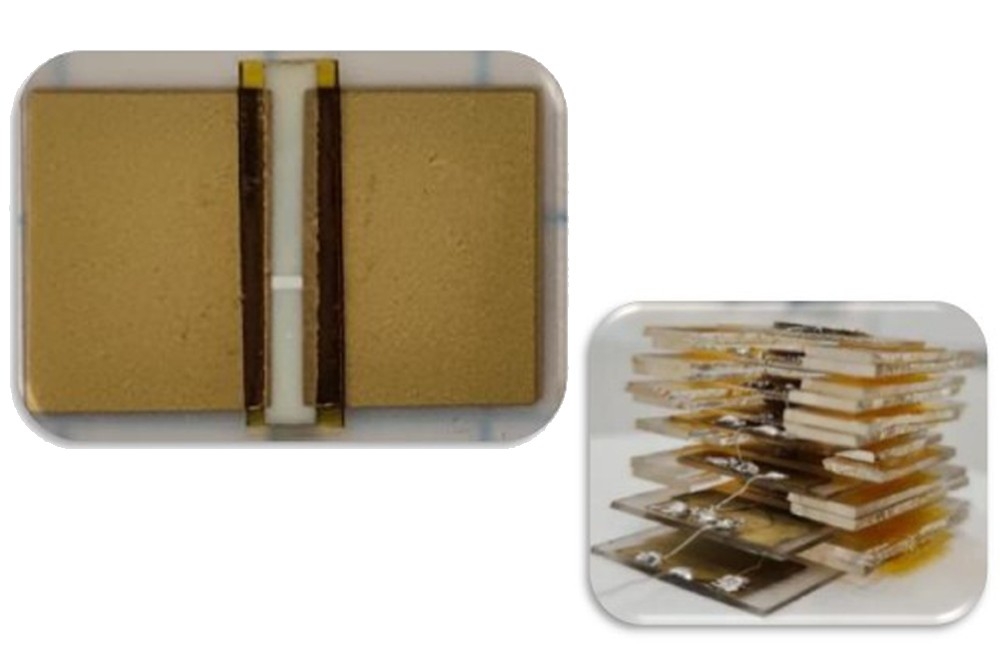

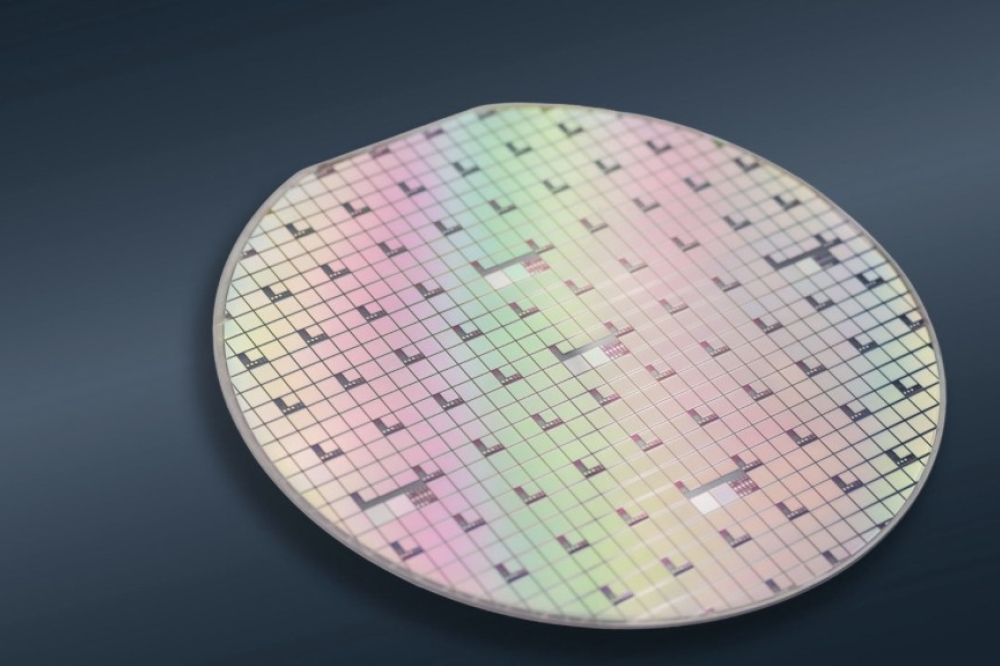

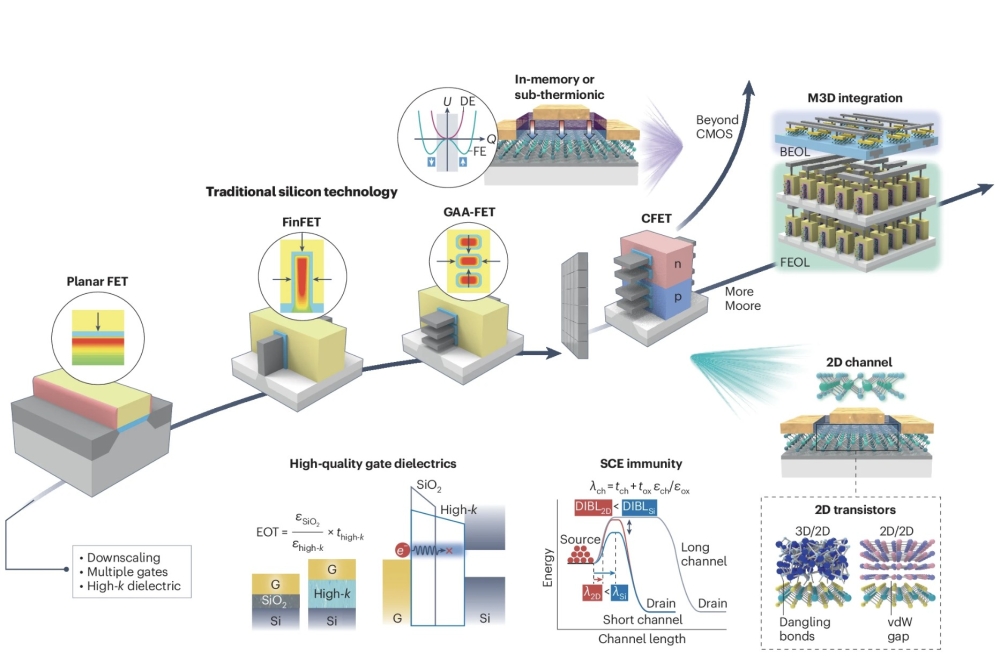

Figure 2. (a) An n-p-n epi-structure on the conventional p-GaN HEMT

platform and a secondary ion mass spectrometry depth profile of

magnesium and silicon dopants. Atomic force microscopy images of the (b)

initial p-GaN surface and (c) GaN surface after n-p-n stack growth on

the E-mode GaN HEMT platform.

The simplicity of this approach has attracted much attention, leading to efforts directed at boosting p-FET performance via strategies that include reducing interface trap states, downscaling the device, and engineering the gate dielectric. But even with these refinements, the current density of the p-FET falls far short of that of the GaN HEMT. This gap in current density between the GaN p-FET and its n-FET sibling poses a significant hurdle for progressing GaN CMOS technology.

Limiting the current density of the GaN p-FET is the low conductivity of the p-GaN layer. Due to a considerable effective mass and strong scattering, the mobility of holes is nearly two orders of magnitude lower than it is for electrons. Compounding this issue, magnesium is the only effective dopant available for p-type GaN. Unfortunately, it’s far from an ideal dopant, being held back by a low activation ratio and a deep energy level that restricts the hole concentration in the p-GaN layer to 1018 cm-3. While innovative epi-structure designs involving N-polar GaN, AlN and GaN heterostructures, superlattices, and InGaN insert layers are able to enhance hole mobility or density, these approaches are incompatible with the existing commercial p-GaN gate HEMT platform.

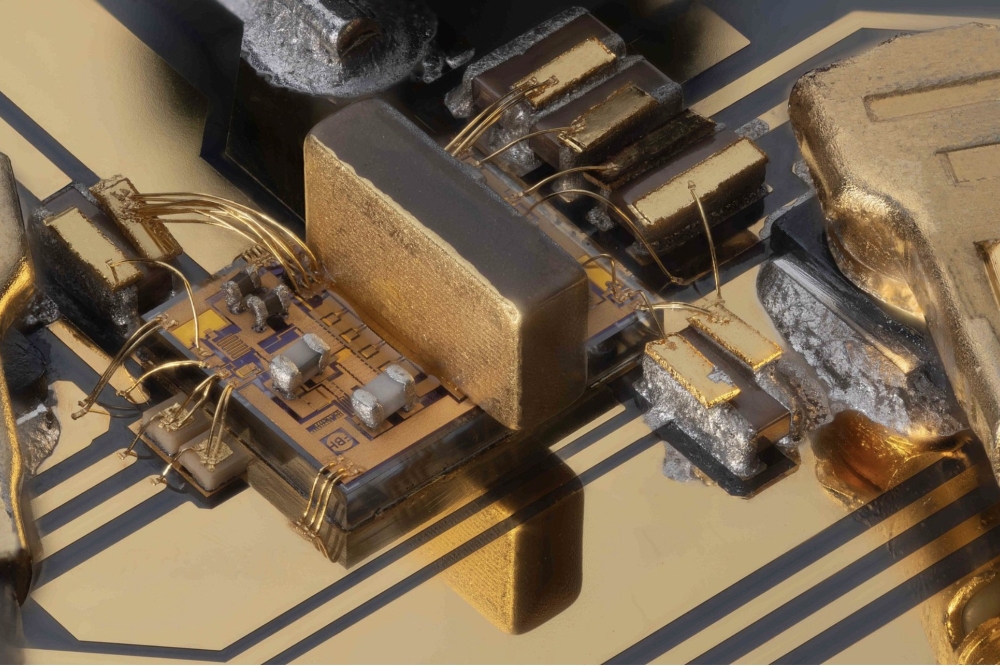

Figure 3. (a) Linear-scale transfer, (b) log-scale transfer and gate

leakage current, and (c) output characteristics of BiPFETs compared with

conventional p-FETs.

To overcome this challenge, our team at the Southern University of Science and Technology is pursuing an innovative GaN p-FET architecture endowed with a bipolar transportation capability (see Figure 1). This bipolar p-FET (BiPFET) features a conventional p-FET gate for maintaining p-type control logic, as well as an additional n-p-n GaN stack, which functions as a bipolar junction transistor that amplifies the current density. Operating in the on state, the p-channel turns on with a gate voltage below the threshold voltage. In this state, a minor hole current flows through the p-channel, and is injected into the base region of the n-p-n stack, initiating a substantial electron current. With electrons serving as majority carriers, the current density of the BiPFET is no longer confined by holes.

In addition to its remarkable conduction capability, the BiPFET inherently ensures a more stable threshold voltage and a higher drain-to-source breakdown voltage. When in the off-state, the bottom n-GaN region acts as a back-side field plate, extending the depletion region from the p-FET gate to the drain side. Thanks to this there is a more uniform electric field distribution, alleviating stress on the p-FET gate and improving the off-state breakdown voltage.

Another advantage of the BiPFET technology is that it is ready for integration with GaN HEMTs, thereby demonstrating outstanding compatibility and feasibility. The n-p-n stack can be realised through MOCVD growth, and the process flow of the BiPFET aligns well with that of the standard p-GaN gate HEMT. These strengths underscore the promising potential of the BiFET for the development of all-GaN ICs.

Figure 4. (a) Off-state leakage current and breakdown characteristics of

(a) the conventional p-FET and (b) bipolar p-FET. Plots of pulsed drain

current as a function of gate-source voltage (ID-VGS) of (c) the p-FET and (d) the BiPFET measured with various drain-source stress voltages (VDS_stress).

Demonstrating the concept

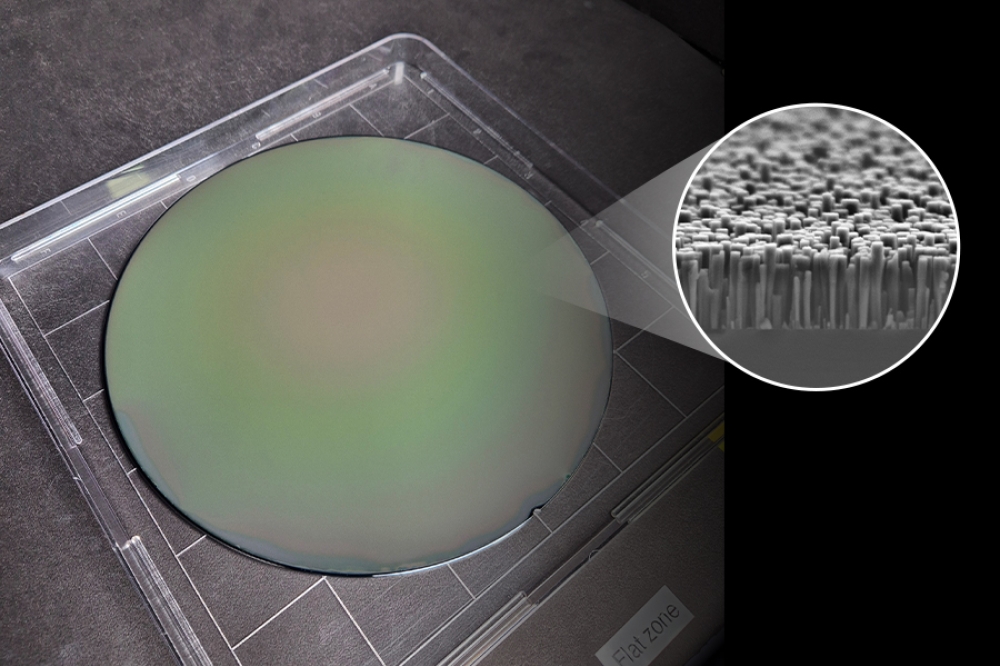

We have investigated the capability of our BiPFETs by producing these devices from a commercial p-GaN HEMT platform featuring a 4.2 µm-thick GaN buffer layer, a 420 nm-thick undoped GaN channel layer, a 15 nm-thick Al0.25Ga0.75N barrier layer, and a 75 nm-thick p-GaN layer with magnesium doping at a concentration of 2.5 × 1019 cm-3. Using this platform, our partners at Suzhou Institute of Nano-tech and Nano-bionics, Chinese Academy of Sciences, led by Qian Sun, selectively grew the n-p-n stack by MOCVD. This stack comprises a 150 nm-thick bottom n-GaN collector layer with a silicon doping concentration of 3×1018 cm-3, a 130 nm-thick n-GaN layer with a silicon doping concentration of 5 × 1017 cm-3 to enhance voltage blocking capability, an 80 nm-thick p-GaN base layer with a magnesium doping concentration of 2 × 1019 cm-3, and a 70 nm top n-GaN emitter layer with a silicon doping concentration of 1019 cm-3 (see Figure 2(a)).

Note that we insert a 100-nm undoped GaN layer between the bottom n-GaN and p-GaN layers to mitigate the impact of the magnesium memory effect. Encouragingly, this n-p-n epi-stack preserves the favourable surface morphology of the original p-GaN, with clear atomic steps (see Figure 2(b) and (c)).

The fabrication of our BiPFETs starts with two-step etching, using a chlorine-based inductively coupled plasma recipe. The first step involves etching the collector region to remove the n-GaN layer, part of the p-GaN base layer, and then the hard mask SiO2 in the p-FET region. During the second step, we simultaneously etch the top n-GaN in the p-FET region and the remaining p-GaN in the collector region until we reach the target depth. After removing the hard mask, we activate dopants in the p-GaN layer by annealing our samples under nitrogen gas at 750 °C for 30 minutes.

Following dopant activation, we add p- and n-ohmic contacts. To ensure an excellent p-ohmic contact on the etched p-GaN surface, we sputter a 50 nm-thick layer of magnesium on the contact region, prior to annealing at 600 °C, to diffuse this metal into the GaN layer. After removing the annealed magnesium layer, we form p-ohmic contacts with conventional evaporation and annealing processes.

According to electrical measurements, the contact and sheet resistance for our p-ohmic contacts are 57 Ω mm and 65 kΩ/sq, respectively. These values are comparable to those for a fresh bare p-GaN layer without any etching.

Our next step is to form n-ohmic contacts on upper and lower n-GaN layers through photolithography, evaporation, lift-off, and annealing.

Following contact formation, we undertake slow inductively coupled plasma etching to gradually recess the gate trench. By going slow, we minimise plasma-induced damage. Then, using atomic layer deposition, we add a layer of Al2O3 that is approximately 22 nm-thick and serves as the p-FET gate dielectric. Evaporation of the gate electrodes follows, before we finalise the fabrication by defining contact vias and probing pads.

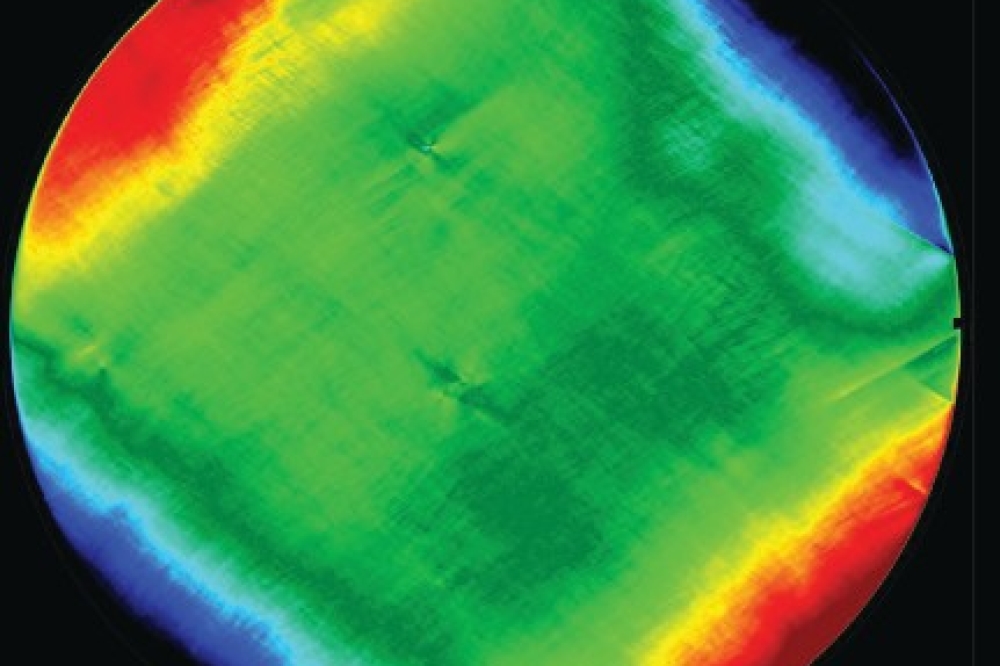

Figure 5. (a) Transfer and gate leakage, (b) output and (c) off-state

leakage characteristics of the E-mode p-GaN gate HEMT on the same

platform with the BiPFET.

Improved current density

By integrating the n-p-n stack into the p-FET, we realise a substantial increase in the current density of the GaN p-FET. With identical MIS-gate dimensions as the p-FET, our BiPFET delivers a 17-fold hike in current density to more than 100 mA mm-1 (see Figure 3). This enhancement in current density is particularly pronounced when comparing output characteristics.

It’s worth noting that this substantial increase in current density is realised without compromising the performance of the MIS-gate. Our BiPFET maintains a high current on-off ratio and exhibits a low gate-leakage current, signifying the well-preserved performance of the MIS gate (see Figure 3(b)). With moderate device scaling, we anticipate an increase in current density.

… and enhanced stability

As well as significantly enhancing the current density, the incorporation of the n-p-n stack offers the additional advantage of mitigating the voltage drop on the p-channel MIS-gate. When operating in the off-state, a depletion region forms in the reversely biased p-GaN/bottom n-GaN junction, creating a depletion region that homogenises the electric field distribution and alleviates stress on the MIS gate. The introduction of the n-p-n stack elevates the off-state breakdown voltage from 22 V to 68 V (see Figure 4(a) and (b)).

The strengths of our BiPFET extend to exhibiting a more stable threshold voltage under pulsed drain-bias stress, a merit that’s attributed to a reduced voltage stress on the p-channel MIS gate. Pulsed tests, conducted on both the p-FET and BiPFET, show that the latter has a significantly lower drain-induced threshold voltage shift (see Figure 4(c) and (d)). In the BiPFET, the n-p-n stack shares the drain stress and safeguards the gate region. Even under a high drain stress of up to 20 V, we do not uncover any degradation in our pulsed transfer curves.

Integration capability

To assess the integration capability of our BiPFET, we concurrently fabricated a p-GaN gate HEMT on the same epitaxial wafer. This p-GaN gate HEMT demonstrates E-mode operation and a high on-off ratio, confirming the continued activation of the p-GaN layer after regrowth of the n-p-n stack (see Figure 5(a)).

We measure a saturation drain current density for our fabricated p-GaN gate HEMT of 200 mA mm-1, a value comparable to that of conventional p-GaN gate HEMTs (see Figure 5(a) and (b)). This robust conduction capability indicates that the 2DEG channel is not significantly impacted by regrowth of the n-p-n stack.

Another encouraging finding is that after regrowth, the buffer and channel layers still exhibit excellent blocking capability (see Figure 5(c)). The off-state breakdown voltage of the fabricated p-GaN gate HEMT achieves 685 V, validating the feasibility of integrating n-channel devices with BiPFETs for the realisation of GaN CMOS and power ICs.

The key strengths of our BiPFET are its exceptionally high current density and its enhanced stability, attributes that enable this class of transistor to be a very promising candidate for seamless integration with GaN HEMTs. This breakthrough paves the way for the design and fabrication of GaN CMOS and power ICs, laying the foundation for tomorrow’s advanced power systems.