Imec integrates InP chiplets on RF Si interposer

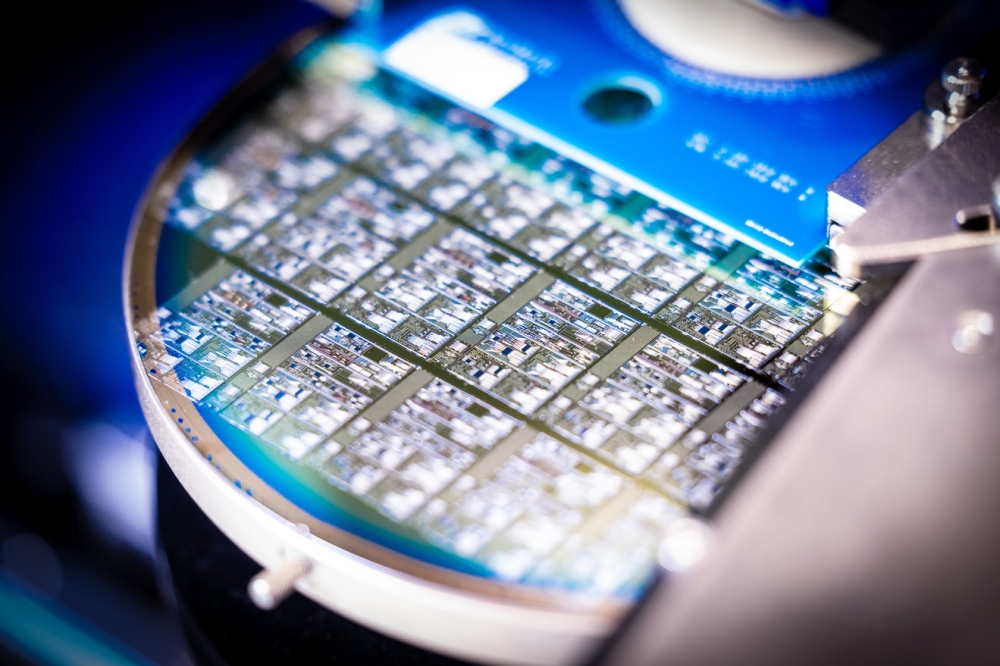

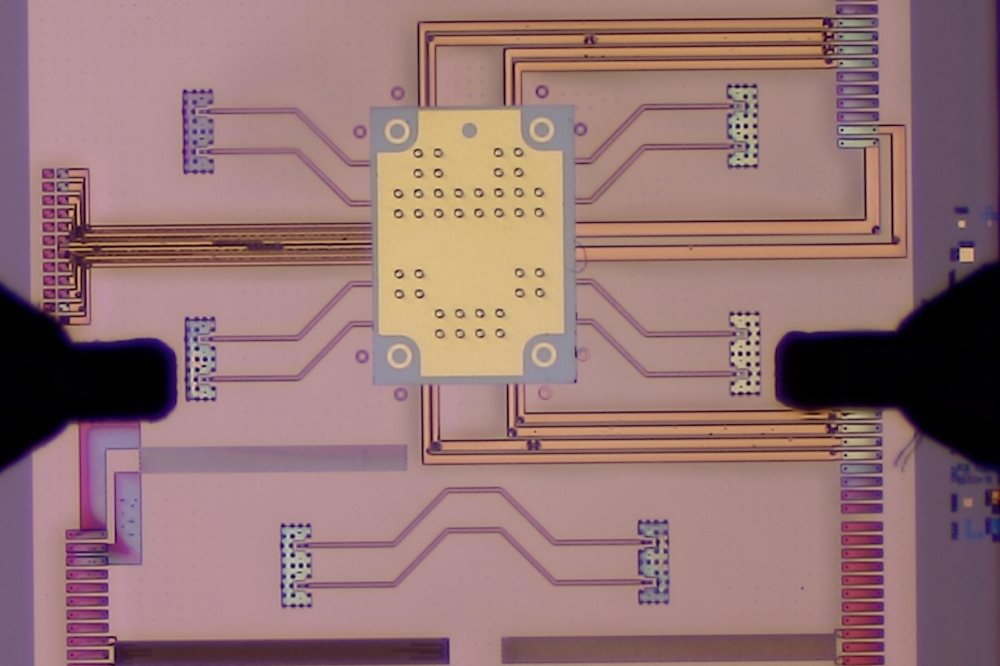

At the IEEE International Electron Devices Meeting (IEDM), Imec is presenting breakthrough results in the hetero-integration of InP chiplets on a 300mm RF silicon interposer.

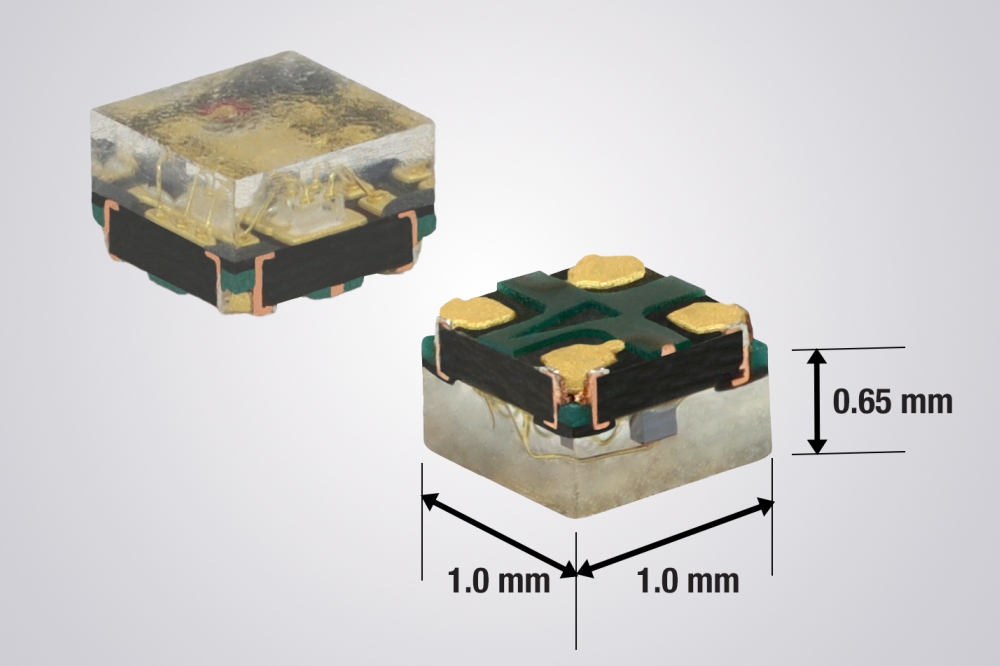

The chiplets’ integration comes with a negligible 0.1dB insertion loss at 140GHz. In addition, no performance degradation is observed upon assembly of a two-stage InP power amplifier (PA). As the first to achieve this, Imec’s findings mark a significant milestone in developing compact, energy-efficient modules for above 100GHz communication and radar sensing.

To meet the demand for faster data transfer, increased bandwidth, and advanced imaging, next-generation communication and (radar) sensing systems must utilise higher frequency bands. This shift requires compact, cost-optimised, and energy-efficient components that operate at higher speeds and deliver more output power than current technologies.

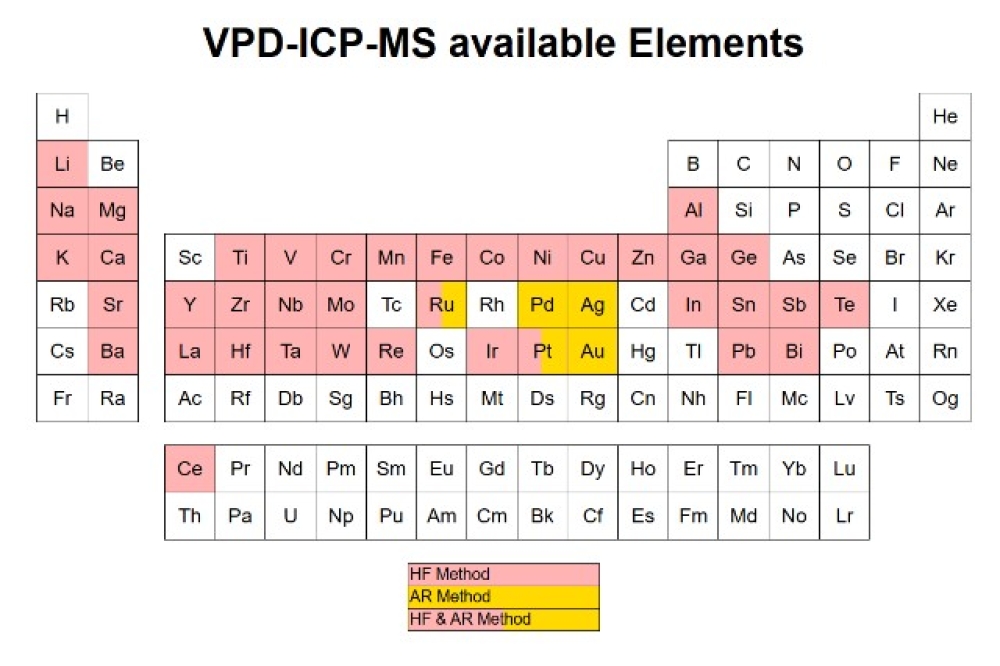

Imec sees heterogeneous III-V/Si-CMOS technology as a promising path forward, with InP showing particular potential thanks to its high gain and power efficiency at mmWave and sub-THz frequencies. However, current InP technology has several drawbacks, such as the use of small-sized wafers and processing via E-beam lithography, while a large portion of the design area is occupied by passives and gold-based backends – limiting InP’s application to niche markets.

“By using InP only where its unmatched performance is essential, Imec is paving the way toward scalable, cost-effective mmWave and sub-THz solutions. This is where a chiplet approach becomes essential,” explains Imec’s Siddhartha Sinha, principal member of technical staff.

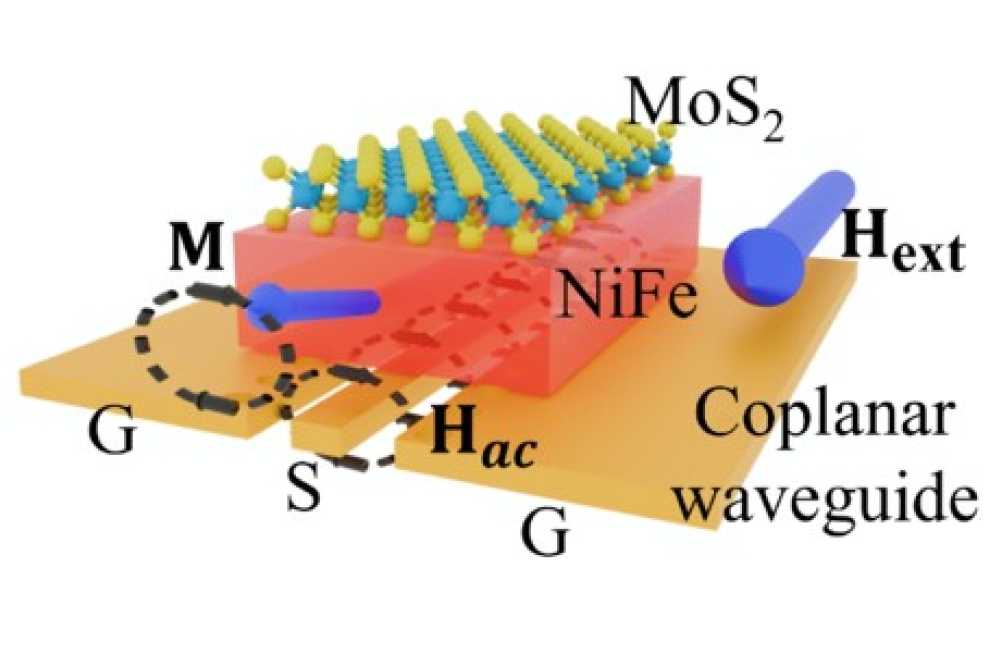

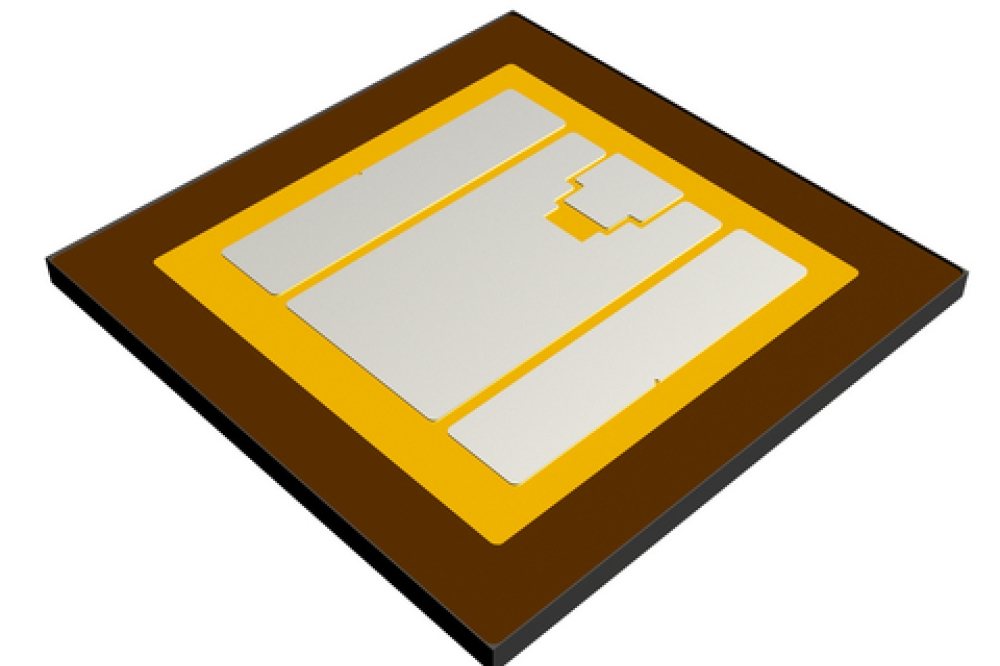

Building on its leadership in silicon interposer technology, Imec has adapted its expertise in 2.5 technology to enable next-gen RF applications, delivering ultra-low loss and compact integration for mmWave and sub-THz signals.

Siddhartha Sinha: “Silicon interposer technology has been pivotal for digital and HPC use cases. Imec has extensive expertise in developing the underlying enablers, such as scaled micro-bumps, high-aspect ratio TSVs, and multi-layer Cu damascene routing to meet these applications’ high-density routing needs. And leveraging this knowledge, we have now adapted silicon interposer technology to also suit RF applications by adding small, high-performance InP chiplets using CMOS-like processes.”

Imec’s RF interposer adds low-loss RF layers on top of a digital interposer to route mmWave signals. Utilising small-footprint interconnects with a 40µm flip-chip pitch, the passive interconnects between the InP chiplets and the RF interposer show a 0.1dB insertion loss at 140GHz – which is negligible. IIn addition, a two-stage InP power amplifier (PA) demonstrates excellent performance with no degradation observed after assembly, validating the effectiveness of the InP chiplet approach.

The path forward

Building on the results presented at IEDM, Imec researchers continue to explore further interposer advancements as part of a broader program to make InP compatible with CMOS processing modules and toolsets.

“In addition to developing a demonstrator for mmWave phased arrays and radar applications, we aim to further shrink the size of the InP chiplets while preserving their superior RF performance. We also plan to add new Si RF interposer features to the platform, including passives like inductors and MIMCAPs, as well as TSV integration and wafer thinning,” says Siddhartha Sinha.

“At the same time, we’re making the platform available to partners for prototyping, allowing them to experiment with Imec’s RF interposer R&D platform,” he concludes.