MCT moves into the next generation of thermal imaging

Most of the devices in military systems are referred to as second-generation thermal imagers. These rely on small arrays (e.g. 4 x 288 pixels) that are scanned across a scene. The need for mechanical devices to scan the detector and the slow build-up of a thermal scene has required the development of a different kind of array. Large-area two-dimensional infrared focal-plane arrays (IRFPAs) stare at a scene, removing the need for mechanical scanning, which reduces power consumption and system size. MCT IRFPAs are now beginning to form the third generation of high-performance infrared imagers. Most of the companies developing IRFPAs are large defense contractors, such as Rockwell and Raytheon. What follows is a look at the technologies that such companies are developing to increase the size and performance and decrease the cost of MCT IRFPAs. The move to growth on silicon The growth of MCT IRFPAs has largely been carried out on bulk CdZnTe (CZT) substrates using a CdTe buffer layer. This places a constraint on the maximum size of the FPA that can subsequently be fabricated because bulk CZT wafers are not available in large sizes, unlike other semiconductors such as silicon. This is one of the main reasons why the growth of MCT onto silicon wafers has become a hot topic of research and development. Array sizes are being pushed ever upwards by the demand for greater image resolution. Little progress seems to have been made in increasing CZT wafer areas above 30 cm2 (4.7 inch2), making the ability to grow MCT on other materials of prime importance. Silicon seems the obvious choice for several reasons. Si wafers are readily and cheaply available in a range of diameters. Costs are driven down by using the cheaper material, but also the larger area means that more FPAs of a given size can be processed on a single wafer. A 4 inch Si wafer gives three times the area of a standard CZT substrate, and moving to 6 inch Si would give seven times the area. Si wafers with diameters at or above 4 inches are also compatible with standard semiconductor processing tools, as developed and used in the Si microelectronics industry, meaning that FPA production can be more easily scaled and automated. The use of Si offers another attraction. The processed FPA must be flip-chip-bonded to Si read-out circuitry. Growing the FPA on Si removes a source of thermal stress as the substrate and read-out circuitry have the same thermal properties. Growth on Si has its problems. CZT has traditionally been used as a substrate because it provides a good lattice match to CdTe and MCT. The growth of MCT onto Si results in a large dislocation density because of the 19% lattice mismatch. Work to reduce this has focused on using thick CdTe/CZT buffers, allowing strain relaxation before MCT growth commences. State-of-the-art dislocation densities for MCT on Si are now around 106/cm2. This is still an order of magnitude more than that found when growing on CZT, but, despite this, MCT array performances have been on a par with those achieved through growth by MBE or LPE on CZT. Currently, MCT growth on CZT substrates is done by liquid-phase epitaxy (LPE). This technique does not lend itself to growth on Si for a variety of reasons. The preparation of the Si substrate requires it to be heated to a high temperature in the reactor to desorb the surface oxide, leaving a clean Si surface that is highly reactive. Unlike MBE, LPE is not a UHV technique making it relatively "unclean". The reactive, oxide-free Si surface will be exposed to impurities that will affect subsequent epitaxial growth. Detector structures are also becoming more complicated, requiring the increased use of thinner layers to improve array performance and flexibility. LPE is not suited to the growth of such layers.

Current state of growth on silicon A group from Raytheon Infrared Operations and HRL Laboratories (Varesi et al.) has reported work on large-format MWIR FPAs fabricated from MCT grown by MBE on 4 inch Si substrates. The defect etch pit density of the MCT was 1-7 x 106/cm2, with fewer than 1000 voids per square centimeter. The variation in x value from the center of the wafer to the edge was found to be 1-4%. Although an order of magnitude more than LPE growth on CZT, this defect density was found to be acceptable for high-performance mid-wave infrared (MWIR) device fabrication. The structure used was based on standard LPE-grown structures with a ZnTe/CdTe buffer layer to prevent defects propagating into the active region (figure 1). 128 x 128 pixel arrays were fabricated, each pixel being 40 x 40 µm. Cd x values were varied in different growth runs from 0.23 to 0.3 to give a MWIR cut-off from 4.8 to 6.4 µm at 140 K. Spectral response curves were found to have a typical shape, regardless of cut-off wavelength, giving a uniform response across wavelengths below the cut-off point. Quantum efficiency, measured at 140 K at 4.0 µm for an active layer with an x value 0.3, was found to be 69%. The maximum reported value for MCT on CZT is 79%. It is thought to be lower on Si because Si reflects a larger portion of the incident MWIR radiation than CZT. Though 1/f noise was found to be higher than in LPE material as a result of higher defect density, the observed 1/f noise is not the dominant contributor to overall FPA noise and so is not having a large detrimental effect on the array performance. Overall FPA performance was tested on both 128 x 128 and 640 x 480 (20 µm unit cell) arrays and compared with arrays fabricated in InSb MWIR detector technology. Despite operation at higher temperatures and without an antireflection coating, the MCT/Si arrays gave comparable performance. Buffer layers for growth on silicon Efforts to reduce the dislocation density in MCT grown on Si are concentrated on the all-important buffer layer. Scientists at Army Research Laboratories and the Night Vision and Electronic Systems Directorate (NVESD) are claiming significant progress in this area through a systematic study of buffer layer growth parameters (Almeida et al.).

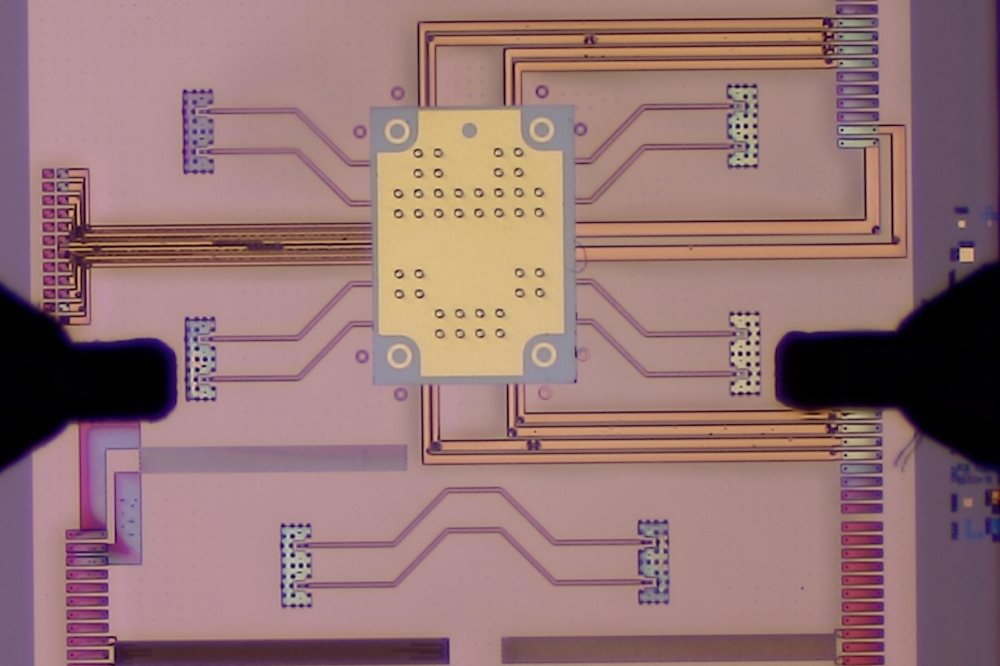

Growth by MBE on Si is typically done by growing a thin ZnTe layer followed by a thin CdTe layer and annealing at about 380 °C under a Te2 flux. CZT growth then proceeds by introducing a flux from a ZnTe cell to the flux from the CdTe cell. This produces surfaces with faceted pit defects with a density of 105-107/cm2, which become replicated in the subsequent MCT layer. It was found that lowering the growth temperature and raising the CdTe flux reduced the defect density, which points to the faceted pit formation being the result of excessive evaporation from the CZT surface at elevated temperatures. Optimization of the growth rate and temperature gave pit densities lower than 200/cm2. A growth rate of about 1 µm/h and temperature less than 290 °C were required to maintain good morphology. Crystalline quality was improved by using a cyclical thermal anneal. Because of the high temperature involved (about 380 °C), a Te2 overpressure of 2 x 10-6 mbar was used to suppress the formation of pits by evaporation of the CZT. Using this anneal reduced the pit density from 1-3 x 107/cm2 to 2-8 x 106/cm2 for a buffer layer 12 µm thick. The lowest density observed was 8 x 105/cm2 for a 20 µm buffer. MBE growth A second group from Raytheon Infrared Operations and HRL Laboratories (Maranowski et al.) reported the first growth of a p-on-n MCT detector structure on a 4 inch Si substrate. To date, much of the work has concentrated on 3 inch substrates. As the need to reduce costs and increase array sizes drives the move to 4 inch substrates, a move to larger MBE reactors is also necessary. A thorough understanding of how growth parameters affect uniformity and defect density is critical to the further scaling of MBE to accommodate larger substrates. The group has investigated this in the course of refining its p-on-n structure. The buffer was formed by depositing 1 µm of ZnTe (to preserve substrate orientation before CdTe deposition) followed by a 6-9 µm CdTe layer. The MCT junction layers are grown on the buffer and consist of a 10 µm MCT:In n-type layer, followed by a 2 µm MCT:As n-type layer. The value of x for all layers grown was 0.3 to give detection in the MWIR region. When growing this structure over a 4 inch diameter area, void defects increased in size and number towards the wafer edge. This was linked to insufficient Hg coverage at the wafer edge, so the void number was lowered simply by increasing Hg flux from the liquid source during growth. Defect etch pit density across the wafer was comparable with state-of-the-art values for growth on 3 inch Si. The study also showed how the Te cell design impacts the stability of the value of x with both layer thickness and distance from the wafer center. Three Te source configurations were used to grow MCT layers, keeping the CdTe cell the same in each instance. Spectroscopic ellipsometry (SE) was used to monitor the Cd x value as layer growth progressed (figure 2). Cell designs B and C gave uniform x-values with time (i.e. thickness), with cell A giving a drift in x of about 0.015 over around 11 hours. Ex situ FTIR measurements of the MWIR layers grown with the different cell designs showed the variation in x-value from the wafer center to the edge. While cells B and C gave uniform x-values with depth, only cell C gave good spatial uniformity also. This shows that MBE source design is crucial to gaining long- and short-term flux stability as well as spatial uniformity. By optimizing Te source design, the x value uniformity on 4 inch substrates was comparable to that from 3 inch substrates. Loophole technology BAE Systems Infrared, UK, has a different approach to two-dimensional MCT arrays from those that have been described so far (Baker et al.). It uses a via hole technology (called loophole technology by the company) as opposed to indium bump bonding for diode read-out. The drivers for developing this approach were noise reduction and the minimization of defective elements. The MCT is grown by LPE on CZT substrates. The loophole process differs because the substrate is removed to allow front surface illumination, which means, therefore, that infrared transmission through the substrate and the quality of the substrate/MCT interface are not issues. Effort can instead be concentrated on producing a very-high-quality MCT region in the center of the wafer. Thermal mismatch between the MCT and silicon read-out circuitry is dealt with by bonding a thin (typically 9 µm) MCT monolith to the silicon circuitry, with the strain arising from thermal expansion is taken up elastically.

One photolithography stage is used to define the mask through which the via holes are etched. This is done by ion beam lithography to expose the aluminum contact pads on the Si read-out circuit beneath. The device is coated with metal and the photoresist removed to leave metal only in the via holes to form a contact between the MCT and aluminum circuit contact below. The process of ion beam milling also crates a junction around the via hole by converting the p-type MCT to n-type by injecting Hg atoms into the lattice, thereby eliminating acceptor-like Hg vacancies (figure 3). A disordered n+ layer 0.5-1.0 µm thick is created with an n-type doping region that decreases exponentially away from the surface for 2-3 µm.