CMOS devices steal show

SiGe bipolar transistors possess sufficient performance to make them well-suited for applications in the emerging 40 Gbit/s optical networking arena. However, like all Si-based bipolar devices, they suffer from relatively low breakdown voltages compared with III-V HBTs. In a novel approach to address this issue, researchers at Philips included an additional layer of SiGe (10 nm with 20% Ge content) in the highly doped part of the emitter, thereby inducing greater Auger recombination which in turn enhances base current without affecting Ic and ft. This increase in base current reduces the gain of the device, which reduces the onset of avalanche breakdown. In essence, this trades gain (ß) against breakdown voltage, where in this case ß is reduced from 2100 to approximately 400 (more than adequate for most applications). As a result breakdown is increased from 2.0 to 2.6 V, representing an improvement of 30%, although this is still much less than can be achieved with GaAs HBTs.

In an attempt to lessen the impact of HBT processing on CMOS fabrication in a BiCMOS process, researchers at IHP in Germany used an "HBT before CMOS" integration scheme. Fabricating the HBT prior to the CMOS portion lessens the thermal budget on the CMOS (in this case a 0.125 µm process), which allows tighter control over source/drain implantation profiles; this in turn improves CMOS performance. However, because this approach increases the thermal load that the HBT experiences during processing, a C-doped base, which is less susceptible to diffusion, is used. The HBTs deliver ft and fmax values of 80 and 90 GHz, respectively, with a breakdown of 2.5 V. Hitachi researchers used small amounts of carbon (up to 0.4%) in the base to compensate for the lattice strain induced by the inclusion of Ge. This reduction in strain reduces B out-diffusion, resulting in sharper doping profiles. The device with 0.4% carbon had ft and fmax values of 124 and 174 GHz, respectively, and a breakdown voltage of 2.3 V, compared with 1.7 V without carbon. In similar work, researchers at Infineon Technologies in Germany used a SiGe:C approach to implement an HBT with ft and fmax values of 106 and 145 GHz, and a breakdown voltage of 2.3 V. IHP has also used carbon in the base to produce devices with ft and fmax values of 100 and 130 GHz, and a breakdown voltage of 2.5 V. The IHP process is relatively simple and does not require an epitaxially buried sub-collector or deep trench isolation, making it attractive for commercial applications.

While carbon incorporation has improved SiGe bipolar device performance, simple scaling and reduction of parasitics results in substantial performance improvements. For example, Conexant demonstrated a 0.15 µm emitter design exhibiting ft and fmax values of 170 and 160 GHz, with a breakdown voltage of 2.0 V. This SiGe bipolar process has been merged with a 0.18 µm CMOS process that uses six layers of metal.

Even though many of these results are not reflective of the SiGe bipolar devices in commercial production, such devices continue to show performance improvements. IBM s latest commercial SiGe BiCMOS process uses a 0.2 µm emitter and exhibits ft and fmax values of 117 and 100 GHz, with impressive noise figures of 0.4 dB at 3 GHz and 0.6 dB at 10 GHz. These bipolars are merged with a 0.18 µm CMOS process in which the NMOS exhibits an ft of 80 GHz.

CMOS makes SiGe obsolete

It is often stated that a BiCMOS process utilizing SiGe bipolar technology for high-speed RF requirements, coupled with CMOS for large-scale digital ICs, offers the full range of characteristics required for almost any desired circuit application, and opens the way for system-on-chip applications. However, based on the improvements in the speed and RF capabilities of CMOS reported at IEDM, through aggressive scaling and a wide range of novel processing developments, many of these advanced CMOS processes could eliminate the need for a SiGe bipolar component. Using a 70 nm cobalt silicide gate, coupled with a body-tied partially-depleted SOI CMOS process featuring dual offset-implanted source-drains to minimize parasitics, researchers at Mitsubishi have developed a CMOS process with RF characteristics that rival those of the SiGe bipolars presented at this year s IEDM. The Mitsubishi devices exhibited ft and fmax values of 114 and 135 GHz, and a gain of 11 dB at 40 GHz.

An SOI approach certainly improves RF characteristics through the reduction of parasitic capacitive coupling to the lossy Si substrate. However, the buried oxide impedes thermal dissipation through the conducting Si substrate, which can be a limitation for power RF applications. With that consideration, researchers at Philips have addressed RF improvements not through the reduction of substrate capacitive coupling using an SOI substrate, but through the reduction of gate resistance. Based on a commercial 0.18 µm CMOS process with a conventional Si substrate, the unit cell uses a novel folded RF-NMOS layout that significantly reduces gate resistance, while the shared drains in the device reduce junction capacitance. In addition, p+ guard rings are used to suppress the pick-up and injection of substrate noise. The resulting gate resistance is a relatively low 4 Ω/square, producing an NMOS device that exhibits ft and fmax values of 70 and 150 GHz, and a noise figure of less than 1.0 dB for frequencies up to 8 GHz. What makes these characteristics so remarkable is that the devices are fabricated with a conventional CMOS process (using commercially available geometries) and are able to deliver SiGe bipolar-like performance.

By combining a parasitic-reducing SOI substrate, reduction in gate resistance using an Al overlay gate approach, and a small gate length of 80 nm, researchers at Fujitsu were able to see even greater improvements in RF performance. The resulting metal overlay gate had a sheet resistance of only 0.02 Ω/square, allowing this device to exhibit ft and fmax values of 120 and 185 GHz, and a noise figure of 0.8 dB at 10 GHz (lower than the Philips results due to the much lower gate resistance). Such performance not only rivals the best results reported for SiGe bipolar processes, but exceeds most GaAs HBT processes and enters the regime that is often thought to be reserved for InP HBTs.

Rather than relying on a metal overlay gate approach, researchers at IBM used very small gate lengths of 40 nm, SOI substrates and aggressive gate oxide scaling (using a gate oxide of only 1.9 nm) in order to improve CMOS performance. The device exhibited ft and fmax values of 178 and 193 GHz - better results than the best SiGe bipolar results presented this year. If this process were combined with the metal overlay gate approach, it is anticipated that such CMOS devices could be pushed through the 200 GHz barrier.

More tricks for CMOS

While aggressive device scaling, SOI substrates, sophisticated gate layouts and source-drain implant profiles, and reductions in gate resistance have produced greatly improved performance, all these approaches should still be considered fairly conventional process refinements. So it is no surprise that CMOS process engineers are looking beyond these approaches to even more radical fabrication techniques to further enhance performance.

In the last year, both IBM and Amberwave have announced the use of SiGe buffer layers in combination with chemical-mechanical planarization (CMP) approaches that permit the growth of strained Si CMOS devices exhibiting enhanced device mobility. Following a similar approach, Hitachi revealed a SiGe virtual substrate process (using a Ge content in the buffer of 30%), which exhibited an extremely low surface roughness after CMP processing of only 0.4 nm (rms). The resulting devices with gate lengths of 0.24 µm showed large increases in mobility of 120% and 42% for electrons and holes, respectively, which translated into improvements in current drives of both NMOS and PMOS devices of 70% and 51%.

Wanting to take advantage of the parasitic reducing capabilities of an SOI approach, while at the same time eliminating the poor thermal behavior, researchers at the Singapore Institute of Microelectronics reported a process to produce a partial SOI platform on a conventional Si substrate. Reactive ion etching (RIE) was used to form a sequence of narrow and deep trenches, in which the upper part of the trenches was passivated by a thin SiO2/SiN layer. The lower portion of the trench was then oxidized by conventional thermal oxidation to form a buried thermal oxide under single crystal silicon regions. This produces regions of SOI structures adjacent to Si-only regions that act as high thermal conductivity pathways to the substrate. Compared with a pure Si bulk process, devices fabricated over the buried oxide regions showed a 56% reduction in output capacitance, a 37% increase in output power for a 2 GHz LDMOS amplifier, and an order of magnitude reduction in drain current. In addition, inductors fabricated over the buried oxide regions exhibited a high Q-factor of 15 at 3 GHz operation.

Silicon on nothing

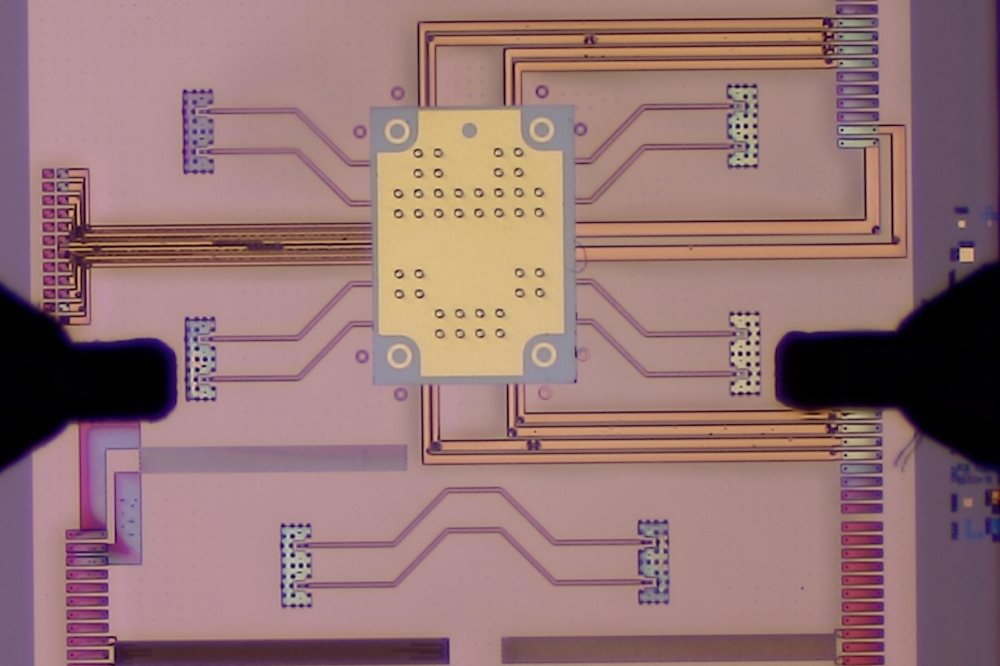

The most novel approach to the reduction of parasitic coupling to the substrate was that reported by Toshiba in the development of a "silicon-on-nothing" (SON) MOSFET using "empty space in silicon" (ESS) technology (see figure 1). The ideal solution to reduce parasitic coupling is not to have a substrate at all, which can be achieved by substrate removal or lift-off. However, in those cases the resulting self-heating and floating body effects of devices fabricated on such membranes render these approaches impractical. Such devices are typically bonded to transfer substrates and then face the same parasitic coupling issues as in conventional device fabrication.

Instead, Toshiba has developed a process to fabricate empty spaces in a conventional Si substrate above which devices can be fabricated. The ESS approach is illustrated in figure 2. Conventional RIE and SiO2 masking techniques are used to fabricate deep trenches. These trenches can be transformed into buried spheres, pipes and plates by H2 annealing at 1100 °C for 3 minutes. During the high-temperature annealing, the trenches close at the surface and form voids beneath. Figure 1 shows a cross-sectional TEM of a fabricated MOS structure above an ESS sphere, where a high degree of crystalline perfection is obtained. This approach should be applicable to any CMOS application, and has the potential of delivering SOI-like device characteristics, while maintaining the high thermal conductivity characteristics of bulk Si wafers.