Technical Insight

Motorola and IQE grow GaAs on large-area Si substrates (Features: Epitaxial Growth)

Motorola, in collaboration with IQE, has demonstrated the growth of gallium arsenide on large-area silicon substrates. This could open the way to low-cost GaAs device manufacturing and a multitude of integration possibilities, writes Marie Meyer.

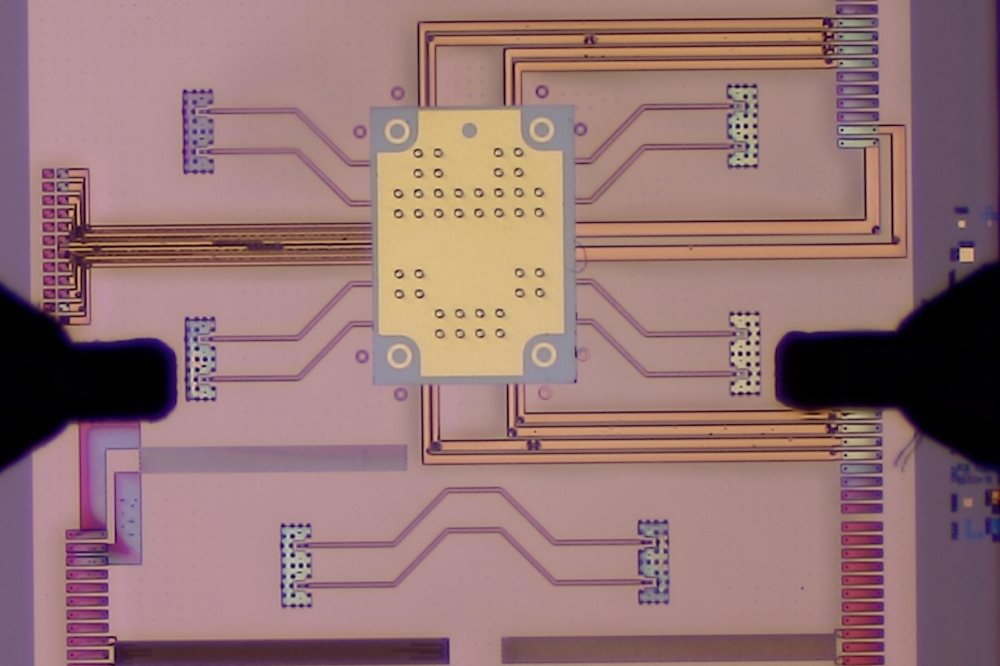

Researchers from Motorola are claiming a breakthrough that may enable GaAs and other III-V compounds to be grown on silicon substrates in a commercially viable manner. This technology could lead to significant cost savings as well as monolithic integration of silicon and compound semiconductor devices, and possibly other new device structures. "It is a really disruptive technology," said Ravi Droopad, a member of the research team at Motorola s Physical Science Research Labs in Tempe, Arizona. Working with IQE, Motorola has already demonstrated 8 and 12 inch GaAs-on-Si wafers that are free from cracks and delamination of the epitaxial layers. Droopad says that work is also being done on the growth of InP, and other materials, on silicon (see ). The key to this new technology is the use of a thin layer of strontium titanate (known variously as strontium titanium oxide, SrTiO3 or STO) between the silicon substrate and the GaAs layer. The STO acts as a compliant buffer layer, reducing the mechanical strain and the thermal mismatch between the epitaxial GaAs layer and the silicon substrate. After the Si-STO-GaAs structure is complete, device structures can be fabricated on top of the GaAs layer using conventional epitaxial growth and wafer processing technologies. "The GaAs layer is thick enough to function as standard GaAs," said Dennis Roberson, chief technology officer of Motorola Labs. "There is no difference whatsoever from bulk GaAs." Motorola has fabricated power amplifiers from the GaAs-on-Si wafers and incorporated them into mobile phones that have been used in live trials. While many other companies have looked at GaAs-on-Si in the past, this appears to be the most successful effort ever reported. Motorola engineers believe the new technology can also be applied to optoelectronic devices such as LEDs and optical communications components. Motorola has filed for more than 270 patents on the technology, and a company spokesperson said that some of the early key applications have been approved, providing the impetus for announcing the breakthrough via a press release on 4 September. Commercialization Padmasree Warrior, a Motorola vice-president, will head-up efforts to commercialize the new technology. She is the former chief technology officer for Motorola s Semiconductor Products Sector (SPS). However, the commercialization effort will not be part of SPS s operations, but will instead be located in a different area of Motorola s corporate structure an interesting fact in light of the widely-circulated rumors that Motorola is trying to sell or spin-off SPS. "Our business model for commercialization is to license the technology broadly into different market segments," said Warrior. She says that Motorola s patent portfolio "covers the whole value chain", beginning with the GaAs-on-Si substrate and continuing with epitaxy, device manufacturing, device/module integration, and on up through systems built using the devices. Warrior indicated that Motorola would be exploring licensing opportunities at each of these five levels. IQE, as a development partner, will apparently enjoy a period of exclusivity with regard to supplying epiwafers based on the new technology. Motorola SPS is already working on GaAs-on-Si RFICs, with a goal of having products in the marketplace by 2003. Warrior said that applying GaAs-on-Si as a "substitutional technology" to replace existing parts, primarily on the basis of lower costs, is a logical first step. But what she is really excited about are completely new applications, perhaps some that haven t even been imagined yet. "I believe that the technology s biggest impact will come from new opportunities for integration, building circuits with compound semiconductors and silicon on the same chip," she said. The technology Motorola s approach has succeeded partly because of the 2.3% lattice mismatch between GaAs and single crystal STO. While this is an improvement over the 4% mismatch that exists between GaAs and silicon, Droopad says this fact alone is not enough to be decisive. He notes that dozens of research groups have reported success in growing GaAs-on-Si, employing a variety of buffer layers and other tricks in the epitaxial growth. "The MRS meetings used to have whole sessions on this topic in the 1980 s," he said. However, most of the work was eventually abandoned when it became obvious that the resulting material was not suitable for use in devices. Conquering the lattice mismatch was only part of the problem. The real challenge to be overcome was that the thermal expansion coefficients of GaAs and silicon differ by almost 50%. As a result, when GaAs is grown directly on silicon substrates, significant numbers of defects, or even cracks, occur when the structures are cooled from the growth temperature to room temperature. Droopad says that Motorola s work began two years ago. The original project was an investigation of STO as a possible replacement for SiO2 in CMOS devices (see Compound Semiconductor September 2001, p35 for details of related work). The team observed that during the growth of the STO layers, oxygen atoms tended to diffuse down toward the Si-STO interface, resulting in an amorphous SiOx layer. The lattice mismatch between STO and silicon is 1.7%. One of the Motorola researchers, Jamal Ramdani, realized that the amorphous layer removed the strain from the STO, allowing it to relax back to its natural crystal lattice constant. When GaAs is grown on the STO layer, it "sees" only the single crystal lattice of the buffer material (). At the same time that this discovery was being made, there was a great deal of interest in the scientific community about "compliant" substrates that could accommodate epitaxial mismatches. Two models were being discussed: use of a viscous buffer layer that allows the substrate to be elastically compliant with the epilayer; and use of a thin twist-bonded layer that plastically deforms to adopt the epilayer lattice. Both models rely on bonding technology, which can be expensive and complex, so the Motorola team began wondering if the amorphous layer might be a way to achieve the same effect without wafer bonding. The results thus far seem to indicate that it can. Both Droopad and Tom Hierl of IQE say that the 8 and 12 inch wafers they have grown using this new technique are visibly superior to any previous attempt at GaAs-on-Si growth they have seen; there are no visible cracks or bowing, and no sign of the epitaxial layer peeling away from the silicon substrate. They report that the defect densities are comparable to those found in homoepitaxy of GaAs on LEC GaAs substrates, and Motorola has successfully run samples through their processing lines at the SPS division. The exact role that the amorphous SiOx layer plays is not yet understood. But it is believed that it is sufficiently compliant to the materials on either side of it to "soak up" the thermal and mechanical strain in the structure. Droopad says that the amorphous layer is "very pliable, very accommodating" to the stresses around it. Extending the technology to other III-V materials (for example, InP-on-Si or GaN-on-Si) will require substituting another perovskite material for the STO layer, in order to achieve a more suitable lattice constant. Droopad says that the STO layer is "very thin," and Hierl adds that this is an important key for economic viability. The STO layer is epitaxially grown in the same molecular beam epitaxy (MBE) chamber as the subsequent GaAs growth, using elemental strontium and titanium in standard effusion cells. Oxygen is introduced through a leak valve. While strontium evaporates readily (at a comparable rate to antimony), titanium has a fairly low vapor pressure, requiring the use of very high temperatures and slow growth rates. Thus the thickness of this layer has a big impact on the cost of this step of the process. IQE has shown that after the STO and GaAs layers have been grown, the wafer can be removed from the MBE system and transferred to a different reactor MBE or MOCVD where it can be used as a substrate for the growth of the same types of III-V layers that can be grown on bulk GaAs substrates. Hierl says it may also be possible to grow the STO layer via MOCVD, but this has not yet been tried. New design considerations? Whether or not the GaAs-on-Si substrates can serve as direct replacements for conventional GaAs substrates is not yet clear. All existing GaAs IC designs were created with the idea of leveraging the semi-insulating properties of undoped GaAs substrates to achieve small parasitic capacitances, good DC isolation, etc. It remains to be seen whether the new technology can provide a substrate with similarly high resistivity (the current samples have a resistivity of 100 .cm, whereas the value for a typical SI GaAs substrate is 108 .cm). If not, steps will have to be taken to make up for this lost advantage. IQE s Tom Hierl indicated that different types of silicon wafers are being evaluated to increase the resistivity of the substrate. In the meantime, Motorola is using low-temperature (LT) GaAs buffer layers. LT GaAs is non-stoichiometric, with 12% excess arsenic atoms. This leads to a significant increase in resistivity, up to 106107 .cm. Droopad says that head-to-head comparisons have been made of conventional GaAs MESFETs and GaAs-on-Si MESFETs with LT GaAs buffer layers, and performance was "95% comparable to commercial FET products". Optoelectronics applications will face the opposite challenge: here it will be necessary to emulate a conducting substrate. Droopad indicated that the most obvious approach would be to dope the STO layer to make it conductive. "STO can be made pretty conductive," Droopad said. "I don t see any major issues in optoelectronics that can t be overcome by engineering." A disruptive technology Conversations with representatives of Motorola and IQE reveal several possible advantages of this new technology provided that it can be successfully commercialized. It could extend the life of current 8 inch silicon fabs, by giving them a cost advantage over 6 inch GaAs fabs, and a performance advantage over CMOS, BiCMOS and SiGe. Only a small re-tooling would be needed to accommodate the new wafers. "The epitaxial growth and the etching process chemistry will be unique to III-Vs," says Droopad, "but all of the other process steps and the wafer handling will be the same as silicon." Monolithic integration of GaAs and silicon devices on the same chip could have long-reaching effects. It may also be possible to extend the technology into non-semiconductor materials. Droopad says Motorola is working on adding PZT (lead zirconium titanate) layers to the GaAs-on-Si stack, to be used for filters and waveguides. Another possibility is BST (barium strontium titanate), a ferroelectric material that could be used to make non-volatile memory circuits. If the technology can be extended to InP, it may be the ideal solution for reducing the costs of integrating and packaging optical components for networking applications. Even if exotic new device types can t be realized, the potential cost savings for conventional III-V devices could still be significant. Several generations of wafer size transitions could be skipped. For RFICs, relative die costs could be reduced by 50% by moving from 6 to 8 inch wafers; the move to 12 inch wafers could reduce them by 75%. For optoelectronic devices, the leap would be even bigger, as they are commonly fabricated on 3 and even 2 inch wafers.