Engineered substrates enhance high-voltage GaN power electronics

Substrates with a ceramic AlN core and a silicon top surface provide a promising platform for the production of high-voltage, fast-switching GaN devices and ICs.

BY KAREN GEENS AND BENOIT BAKEROOT FROM IMEC

Think of an application for SiC power electronics and you’ll probably think of electric vehicles (EVs). After all, it’s the battery-powered automobile that’s driving the growth in sales of SiC MOSFETs, a trend that’s forecast to continue throughout this decade and beyond. Employed in the traction inverter, these transistors tend to operate in systems operating at 400 V – but higher voltages, particularly 800 V, will be introduced over the coming years, a shift that moves towards the sweet spot of SiC. Commercial products associated with of this class of transistor span several hundred volts to a few kilovolts, with the well-established 1.2 kV MOSFET offering ideal headroom for EVs operating with 800 V power systems.

However, SiC is not the only wide-bandgap semiconductor with the attributes needed to make a compelling case for deployment in EVs. There’s also GaN, which many are overlooking today for this application. This attractive alternative is already enjoying tremendous success at lower voltages, and is now the key component in fast chargers. Increasing the blocking voltage to 1 kV or beyond remains a challenge for fabrication of devices on large-area substrates. A possible route to success is turning to engineered substrates, an approach we are pioneering at the European microelectronics research centre, imec. Alternatives such as bulk GaN exist, though they come with smaller wafer diameters and significantly higher cost.

The GaN HEMT has a number of strengths, including a high critical-electric-field and a high electron-mobility, the latter realised in combination with very high density for the two-dimensional electron (2DEG) that’s created at hetero-interfaces with other III-nitrides, such as AlGaN. In recent years, there has been significant improvement in the leading forms of this device, which include the enhancement-mode (E-mode) lateral p-GaN gate HEMT and the cascode depletion-mode (D-mode) HEMT.

To realise high power levels in D-mode devices in a cascode configuration, engineers tend to direct their efforts at lowering the 2DEG channel resistance and increasing the electron channel mobility, steps that result in a very low on-resistance.

In comparison, the E-mode p-GaN gate HEMT has a higher 2DEG channel sheet resistance and thus a higher on-state resistance. However, this weakness must be weighed against a device architecture that allows a higher level of monolithic integration, thanks to the E-mode transistor ensuring a safe stand-alone operation and a simpler gate driving circuitry in many applications.

In addition to these advantages, the p-GaN gate HEMT stands out for its maturity and performance. That’s why we have selected this particular device architecture for the first demonstrator for a 1200 V GaN switch, while exploring the potential of vertical GaN structures for future high-voltage applications.

Engineered foundations

To produce a switch that operates at such a high voltage demands a thicker epitaxial layer, which presents challenges in manufacturing. This is where Qromis Substrate Technology, often referred to as just QST, comes into play.

Qromis’ commercially available, engineered substrates feature a ceramic AlN core that combines a high mechanical strength with close matching of the coefficient of thermal expansion of GaN and AlGaN layers. In addition to these features, the seed layer for the epitaxial growth of the GaN and Al(Ga)N layers remains well-known silicon, with a (111) crystal orientation.

This engineered platform provides a great foundation for the growth of thick, crack-free GaN stacks, significantly reducing the risk of wafer breakage, a common issue when using silicon substrates for growing thicker stacks targeting 1200 V, especially at larger diameters, such as 200 mm.

Using these proprietary substrates, we have fabricated lateral GaN power HEMTs with 9 µm-thick AlGaN buffer stacks that deliver excellent electrical performance. These devices have a hard breakdown voltage of over 1800 V, and a specific on-resistance of around just 5.8 mΩ cm².

Another asset of QST is its scalability. Applicable to 300 mm wafers, this technology is a major step forward for cost-effective, high-volume production. Migrating to larger wafers allows more devices per batch, helping to drive down manufacturing costs and accelerate the adoption of GaN in high-voltage markets.

Vertical or lateral?

Figure 1:Cross-section STEM of (left) the p-GaN gate architecture used in lateral devices and (right) the trench gate MOS architecture used in vertical devices.

One key question when pursuing higher voltages, such as 1200 V or more, is this: which architecture, vertical or lateral, will offer a superior performance? With lateral GaN devices, all connections – that’s the gate, the source, and the drain – are made to the front side. With this geometry, as voltage targets rise, the gate-to-drain distance has to increase to maintain safe operation. In addition, it’s critical to lengthen the field plates – they are employed to distribute the high-voltage in the off-state, with source-connected field plates used to optimise the electric-field distribution (see Figure 1 (a)). Due to these requirements, the introduction of higher blocking voltages requires a larger footprint, and leads to a higher specific on-state resistance and larger capacitance, limiting efficiency and scalability.

To address these issues, a number of researchers, including ourselves, are investigating vertical GaN architectures. Unlike lateral devices, vertical structures distribute the high off-state voltage throughout the thickness of the epitaxial stack, rather than across its surface. Thanks to this, the device footprint remains compact, regardless of voltage rating – a noteworthy asset for high-voltage devices.

A key challenge associated with the development of vertical GaN devices is realising low defect densities in the epilayers. In GaN-based epitaxial stacks grown on foreign substrates – including silicon, employed in all commercially available GaN devices – the most common defects are one-dimensional (1D) dislocation lines perpendicular to the surface. In lateral devices, it appears that these dislocation lines do not have a significant impact on device operation and reliability. However, that’s not the case for vertical devices, where current flow is inherently from bottom to top, and 1D defects interfere with vertical current flow. Due to this limitation, it’s preferable to produce vertical devices using homoepitaxial growth on GaN substrates. But GaN substrates are expensive and limited in size, restricting commercial scalability. One possible avenue for further research involves investigations to understand the full extent of these 1D defects on the operation of vertical GaN devices, as well as determining what 1D defect level may be acceptable regarding device performance and reliability.

Using QST substrates for vertical device development, we have grown thick, high-quality n-type GaN drift layers on 200 mm wafers, paving the way for manufacturable vertical GaN devices. We have produced epitaxial stacks with a thickness exceeding 11 µm on this engineered foundation, enabling robust device performance.

We have processed these epiwafers into semi-vertical trench gate MOSFETs. When these devices are in the on-state there’s an electron inversion channel in a p-type GaN layer, similar to traditional MOSFETs, albeit at the sidewall of the trench MOS gate. During device operation, electrons flow from the source n+-GaN layer through the electron inversion channel towards the deeper drift layer, before they are transported into a buried n+ layer at the bottom of the structure. We use a drain metal contact from the frontside towards the buried n+-GaN layer to collect these electrons.

Vertical GaN devices are emerging as a promising direction for future high-voltage power electronics, attracting significant research interest worldwide. Although still in an exploratory stage, this technology holds potential to overcome key limitations of conventional lateral architectures.

GaN ICs on chip

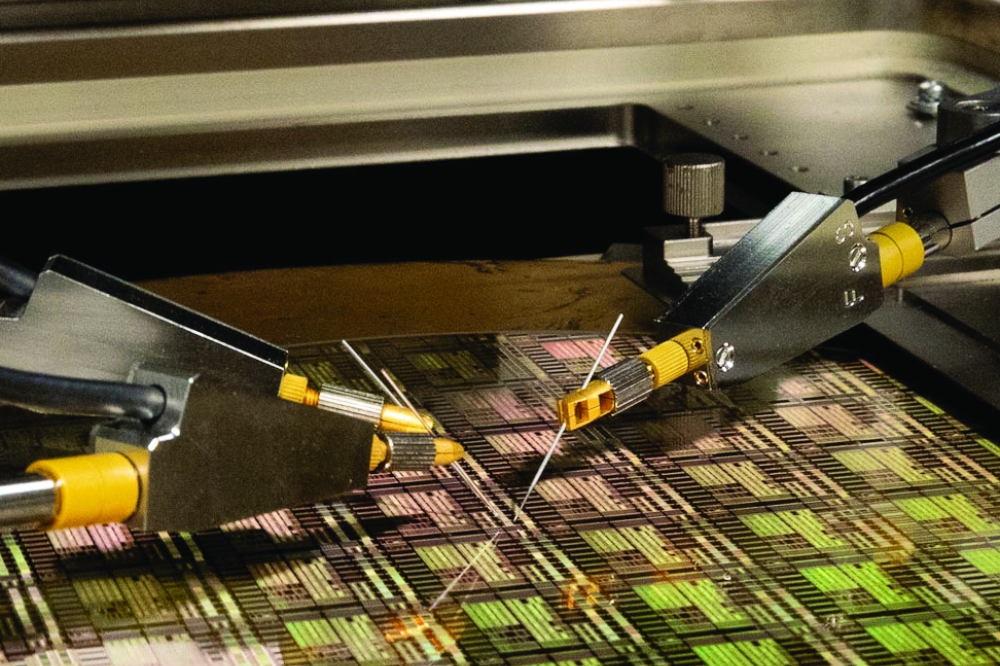

Figure 2: Example of 650 V GaN-on-QST monolithic IC, depicting a symmetrical 140 mm half-bridge with integrated driver and level shifters.

Today, most GaN-based power systems are built from multiple discrete chips, assembled on a printed circuit board. While this modular approach is effective, it introduces parasitic inductances – they are unwanted electrical effects that can degrade performance, especially in fast-switching applications.

A promising route to truly harnessing the speed and efficiency of GaN is monolithic integration – that’s the bringing together of multiple power devices and control circuits on a single chip. GaN power ICs are already finding their way into power supplies, motor drives, and converters, offering compact, high-performance solutions.