Giving GaN a superjunction

Equipping enhancement-mode GaN transistors with a superjunction boosts the blocking voltage beyond 10 kV.

BY JIN WEI AND BO SHEN FROM PEKING UNIVERSITY

Today’s GaN power devices are well-established, generating significant sales in consumer electronics. They are widely deployed to block several hundred volts, with the 650 V enhancement-mode HEMT enjoying wide utilisation.

However, at higher voltages, SiC is seen as the main contender to incumbent silicon power technologies. There are only limited reports of GaN power HEMTs operating at kilovolts, a requirement for serving in high-voltage power grids, rail transportation, and industrial applications. However, GaN has much promise, offering superior theoretical characteristics to its established rivals.

There are two major challenges to address when developing GaN devices for kilovolt applications. One is that the key figure of merit – it’s equal to the square of the blocking voltage, divided by the specific on-resistance – falls far short of what theory suggests. Closing this gap is crucial, as it will allow a GaN power device to attain an equivalent breakdown voltage at smaller device dimensions, and ultimately slash chip costs through substantial miniaturisation. The second issue to address is to tackle the severe degradation in dynamic on-resistance under high-voltage stress that arises from notorious trapping effects – they are particularly prevalent in the kilovolt-range.

A viable approach for enhancing the figure of merit for ultra-high-voltage GaN transistors is to increase the blocking voltage while retaining the gate-to-drain distance, by introducing sophisticated field plates, gate termination extension, surface treatment, or the addition of a GaN cap layer. However, all these solutions suffer from trade-offs associated with processing complexity, reliability, and performance. Due to this, their adoption must be carefully evaluated for target applications.

A promising alternative is the superjunction, an architecture successfully implemented in silicon power devices, where it provides an effective boost to the figure of merit. The superjunction is viewed as a promising candidate for electric-field management and increasing the blocking voltage of GaN power devices. However, it is difficult to implement in enhancement-mode GaN lateral devices.

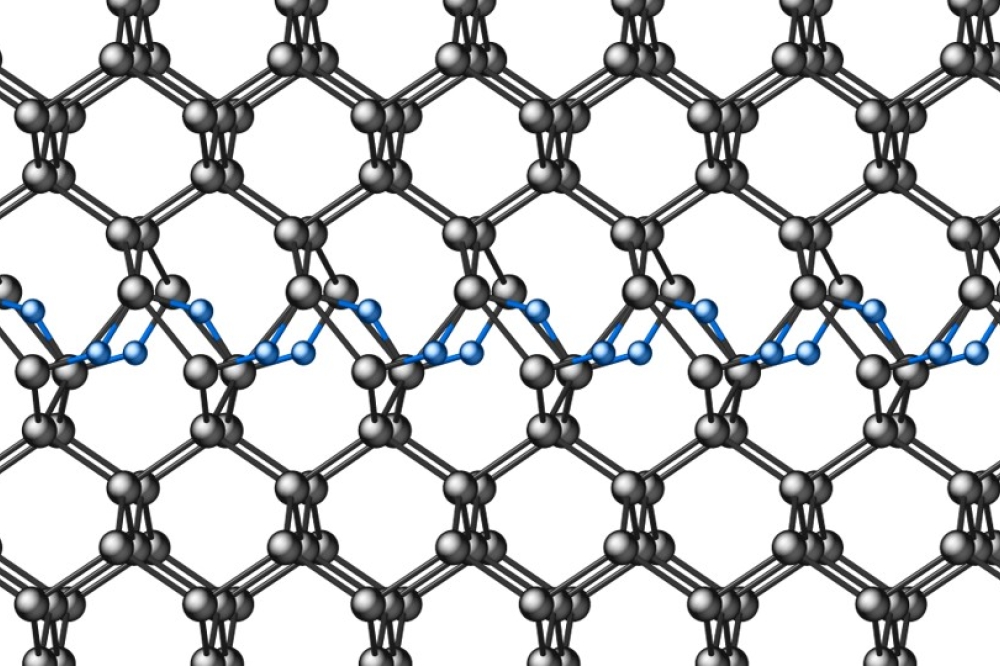

Figure 1. The structure and process flow of the proposed superjunction p-GaN gate HEMT (SJ-HEMT).

GaN superjunction technology

Recently, our team at Peking University has proposed a novel superjunction concept that’s based on a standard enhancement-mode p-GaN gate HEMT platform (see Figure 1).

We fabricate this device using a standard p-GaN gate HEMT epiwafer, resulting in enhancement-mode operation. The superjunction structure is constructed by alternative p-/n-pillars along the direction perpendicular to current flow. The p-pillar is a thinned p-GaN stripe, and the n-pillar is the two-dimensional electron gas (2DEG) stripe between two adjacent p-pillars. The width of p-pillar is fixed to 4 µm, and charge balance is achieved by tuning the lateral width of the 2DEG stripes using photolithography. This approach gives the freedom to study device performance as a function of charge balance.

Devices are produced on a 2-inch GaN-on-sapphire wafer that features a 90 nm-thick p-GaN layer, a 15 nm-thick Al0.2Ga0.8N barrier layer, a 200 nm-thick undoped GaN layer and a buffer layer. Fabrication commences with a partial etch of the p-GaN layer outside of the gate region, and a second etch defines the p-pillars. We then deposit a SiO2 layer by plasma-enhanced CVD at 300 °C, before adding source and drain ohmic contacts, formed from a

Ti/Al/Ni/Au stack annealed under nitrogen gas at 810 °C for 30 s. After this, fabrication turns to fluorine ion implantation for planar isolation and the deposition of a Ni/Au stack for the gate, followed by annealing in oxygen gas to form an ohmic contact to p-GaN. Finally, probing pads are added.

It’s worth noting that the process for fabricating our superjunction HEMT is compatible with that employed for standard p-GaN gate HEMT technology. The superjunction structure can be realised with an additional p-GaN etching process. Thanks to the high degree of compatibility with the process used to make conventional devices, it would be straightforward to produce the proposed superjunction HEMT in existing foundries.

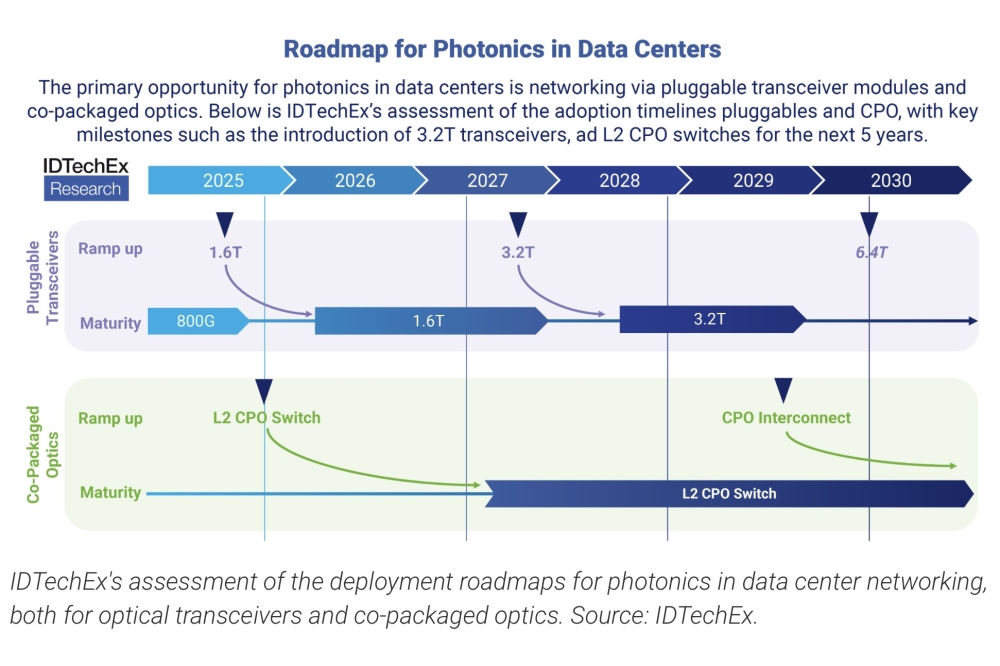

Figure 2. The measured relationship for the blocking voltage (BV ) and n-pillar width (WN) of superjunction HEMTs with different source-to-drain lengths (LGD) when the p-pillar width is fixed at 4 µm. For all source-to-drain lengths, the highest blocking voltage is obtained at WN/WP = 5/4 µm, which is the charge balance point.

Charge balancing

Charge balance is the core feature for all superjunction devices. For our proposed superjunction HEMT, during operation at a low drain stress, p-pillars and n-pillars are mutually depleted and the depletion region expands with drain stress. Meanwhile, at a high drain stress, the p-pillars and n-pillars are fully depleted, inducing a fast expansion of the depletion region. Due to this behaviour, our superjunction HEMT realises a more uniform electric field and a higher breakdown voltage. However, enjoying these benefits is not easy – compared with their silicon siblings, lateral GaN power devices are more involved, with complex charge distributions that can arise through polarisation charges, incomplete ionisation, and internal trapping.

Due to these complexities, the test devices have been developed that are similar to JFETs to characterise the charge balance effect. These transistors uncover the depletion behaviour of n-pillars and p-pillars under reverse bias.

During tests, testing currents through the n-pillar and also the p-pillar are measured. When a negative bias is applied to the p-pillar, a depletion region is formed in both the n-pillar and p-pillar, mimicking the depletion behaviour of the superjunction HEMT. Eventually, the current is cut off as the bias increases, marking the conditions for depletion of the whole n-pillar.

When n-pillars and p-pillars are simultaneously depleted at the same bias, charge balance is realised. This allows specially designed testing devices to provide clear guidance for the charge balance design in GaN power devices. According to measurements, charge balance is realised for a n-pillar width of 5 µm and a p-pillar width of 4 µm. This is a milestone: the first experimental proof for charge balance in GaN devices in the scientific literature.

The charge balance condition has been additionally verified with breakdown voltage measurements (see figure 2). This involved fixing the width of the p-pillar to 4 µm, and investigating the relationship between the blocking voltage and the width of the n-pillar for superjunction HEMTs with various gate-to-drain distances. This study determined that the highest blocking voltages occurs at charge balance, with an n-pillar width of 5 µm, indicating that the charge-balanced point arises at an n-pillar width of 5 µm and a p-pillar width of 4 µm.

Figure 3. Off-state current-voltage curves of (a) conventional p-GaN gate HEMT and (b) superjunction-HEMT with widths of the n- and p-pillars (WN/WP) of 5 µm and 4 µm, respectively. (c) The relationship between blocking voltage (BV) and gate-to-drain distance (LGD).

For the superjunction HEMT with a gate-to-drain distance of 77 μm, the

blocking voltage exceeds 10 kV (the measurement limit), and is projected

to be 11,935 V by linear extrapolation.

Another area of this work involves investigating the breakdown voltages of conventional p-GaN gate HEMTs, as well as our proposed superjunction HEMTs with gate-to-drain distances from 17 µm to 77 µm. For this study, we used charge-balanced superjunction HEMTs with an n-pillar width of 5 µm and a p-pillar width of 4 µm.

This investigation determined that conventional p-GaN gate HEMTs have an average breakdown field – defined by the blocking voltage, divided by the gate-to-drain distance (BV/LGD) – of just 0.91 MV cm-1. The corresponding maximum breakdown voltage is 6,965 V.

In comparison, the performance of the charge-balanced superjunction HEMTs are far more impressive. They have an ultra-high average breakdown field of 1.55 MV cm-1, a figure derived from a breakdown voltage of 6525 V, recorded for a device with a gate-to-drain distance of 42 µm. More significantly, the breakdown voltage of the superjunction HEMT with a gate-to-drain distance of 77 µm is beyond 10 kV – based on linear extrapolation, it is projected to be 11,935 V. As far as we know, this is the first experimental demonstration of an enhancement-mode p-GaN gate HEMT with a breakdown voltage beyond 10 kV, marking a technological milestone for lateral GaN power devices in high-voltage applications.

This substantial enhancement in breakdown voltage opens the door to a significant reduction in gate-to-drain spacing for kilovolt-rated devices, which can simultaneously offer a lower specific on-resistance and a reduction in active area by 20-40 percent compared with conventional designs.

More critically, the charge-balanced superjunction HEMT provides electric-field-profile optimisation, demonstrating a lower peak electric field intensity at equivalent blocking voltages, according to numerical simulations. Thanks to this refinement, reliabilities at high-voltage are expected to be enhanced with the superjunction HEMT, which promises to offer greater robustness to the likes of hot-electron effects, high-temperature reverse-bias stress and current collapse.

Figure 4. An ultra-low dynamic on-resistance/static on-resistance ratio

of 1.5 is obtained in superjunction HEMT after a 6.5 kV drain stress.

Improved performance

The proposed superjunction HEMT has one unique advantage, thanks to having a 2DEG under both the n-pillar and p-pillar contributing to conduction. That’s not the case with the conventional silicon superjunction MOSFET, which has just the n-pillar contributing to conduction.

When in the on-state, the 2DEG under the p-pillar can be generated by field effect, when the p-pillar is directly connected to p-GaN gate. According to transfer length measurements, sheet resistances under the n-pillar and p-pillar are 416 Ω/sq and 411 Ω/sq, respectively. Therefore, there is no degradation to the on-resistance of superjunction HEMTs. The fabricated superjunction HEMT with a gate-to-drain distance of 77 µm has a threshold voltage of 0.9 V, defined at a drain current density of 10 mA mm-1, meeting the requirement of enhancement-mode operation for power systems. The corresponding on-resistance is 36.4 Ω mm – defined at a drain-source voltage of 1 V and a gate-source voltage of 3.5 V – corresponding to a specific on-resistance of 32.03 mΩ cm2.

For conventional GaN HEMTs, one of their weaknesses is a degradation in dynamic on-resistance that stems from the intrinsic trapping-induced negative charge storage. This is to blame for unexpected power loss.

Note that this is not an issue in superjunction HEMTs, which benefit from a combination of: surface traps above the p-pillar being effectively screened by holes in the p-pillar; and the recovery of traps, effectively accelerated by hole injection/light emission. Due to these benefits, the superjunction HEMT with a gate-to-drain distance of 77 µm exhibits an ultra-low ratio of dynamic on-resistance to static on-resistance – it’s just 1.50, after off-state stress up to 6500 V.

Based on these results, one can conclude that the proposed superjunction HEMT, which is capable of enhanced stability and reliability, offers great potential for serving in kilovolt applications. As far as we know, this study provides the first report of dynamic on-resistance of GaN power HEMTs with a drain stress of up to 6.5 kilovolts. This demonstration paves the way to ultra-high voltage applications using GaN transistors, with results confirming that the proposed superjunction HEMT technology overcomes the critical reliability barrier for practical kilovolt-level GaN devices.

Figure 5. Benchmark for the specific on-resistance as a function of

breakdown voltage for superjunction HEMTs and state-of-the-art

high-voltage (more than 2 kV) GaN power transistors.

Compared with state-of-the-art high-voltage GaN power HEMTs, the superjunction HEMT provides best-in-class performances, with a figure of merit of 3.81 GW cm-2 at a gate-to-drain distance of 42 µm. For the variant with a gate-to-drain distance of 77 µm, blocking voltage exceeds 10 kV, realised while maintaining a specific on-resistance of 32.03 mΩ cm2. The associated, projected figure-of-merit is 4.45 GW cm2 – a landmark achievement that redefines the potential performance of single-channel GaN HEMTs.

More significantly, the superjunction HEMTs offer a high degree of fabrication compatibility with conventional devices, and feature a natural single-channel planar structure, facilitating the development of a high-voltage integration platform. These advances are a critical step towards bridging the gap between theoretical material potential and practical device performance in ultra-high-voltage GaN technology.